什么是MOS的體效應(body bias)

通常,我們將MOS管視為一個三端器件,包括柵極、源極和漏極。然而,襯底是其隱藏的第四個端子。下圖為一個nMOS,g、s、d、b分別代表柵極、源極、漏極和襯底。

上圖為以nMOS為例,簡述其關斷、線性區和飽和的條件

絕大多數情況下,設計將襯底和源極連在一起,但是有時候出于性能考慮(如在芯片工作模式下實現高Ion和在芯片睡眠模式下實現低Ioff)會通過施加體偏置來動態調整晶體管的閾值電壓。大多數情況下我們將閾值電壓(Vt)視為常數。然而,Vt隨源極電壓的增加而增加,隨襯底電壓的增加而減小,隨漏極電壓的增加而減小,并隨溝道長度的增加而增加 。

進入正題:體效應 (body bias)簡介

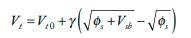

當在源極和襯底之間施加電壓Vsb時,它會增加反轉溝道所需的電荷量,從而增加Vt。Vt可以建模為:

其中Vt0是襯底連接到源極時的閾值電壓,φs是閾值時的表面電位(有關表面電位的進一步討論,請參閱 [Tsividis99] 等器件物理學著作),γ是體效應系數,通常在0.4到1V^(1/2)的范圍內。這些參數具體值取決于溝道中的摻雜水平。體效應會進一步降低傳輸弱值(例如,nMOS傳輸“1”,前文提到的nMOS可以傳輸強“0”弱“1”)的直通晶體管的性能,下文將描述如何有意施加體偏置來改變閾值電壓,從而在性能和亞閾值漏電流之間進行權衡。

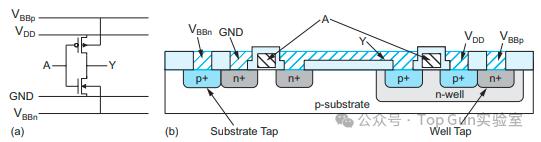

上述公式可簡化為:

從公式可知,通過調節Vsb可以調制閾值電壓Vt,這就是利用了體效應的特性。體效應的用途舉例:可以使用低閾值電壓 (low-Vt) 器件,并在芯片睡眠模式期間施加反向體偏置 (RBB:reverse body bias) 以減少漏電流,體偏置可以施加到電源門控晶體管上,以便在芯片睡眠期間更有效地將其關閉;或者,可以使用高閾值電壓 (higher-Vt) 器件,然后在芯片工作模式期間施加正向體偏置 (FBB:forward body bias) 以提高性能。

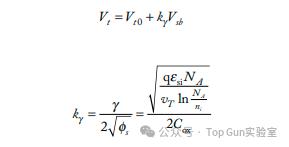

施加體偏置需要額外的電源軌來分配襯底和阱電壓。例如,對于1.0V n阱工藝,RBB方案可以將p型襯底偏置在VBBn=–0.4V,將n阱偏置在VBBp=1.4V。

體效應 (body bias)的可靠性風險

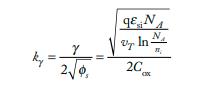

由下面這個公式可推導出,體效應隨著柵氧化層厚度 (tox) 變薄而減弱。

可靠性風險總結:

1、 如設計中沒有妥善管理因體效應增加的漏電流,可能會導致芯片功耗過高,甚至引發熱失控等問題

a)帶間隧穿 (BTBT) 引起的結漏電流:施加過大的反向體偏置(例如,低于-1.2V)會導致通過BTBT效應產生更大的結漏電流,從而增加功耗并影響器件性能。

b)體到源二極管電流:施加過大的正向體偏置(例如,高于0.4V)會導致大量電流通過體到源二極管,這也會增加功耗并可能導致器件損壞。

熱載流子注入 (Hot Carrier Injection, HCI):這是最主要的可靠性問題之一。施加反向體偏壓會增強溝道內的電場,加速電子獲得能量成為“熱載流子”。這些高能載流子會注入并損傷柵極氧化層,導致晶體管的閾值電壓發生漂移、跨導下降和驅動電流減小,從而使器件性能隨時間推移而退化,最終導致電路失效。b)偏壓溫度不穩定性 (Bias Temperature Instability, BTI): 在高溫和電場共同作用下,柵氧化層與半導體界面處會產生陷阱電荷,導致閾值電壓漂移。體偏壓,特別是反向體偏壓,會加劇電場強度,從而加速BTI效應,縮短器件的可靠運行壽命。c)應力導致的性能退化: 持續施加反向體偏壓會增加器件內部的應力,長期下來可能導致器件性能退化,例如擊穿電壓的降低。

總而言之,體偏壓是一把“雙刃劍”。它為現代集成電路設計提供了在性能和功耗之間動態優化的強大工具,但設計者必須仔細評估并緩解其帶來的可靠性風險,如熱載流子效應、BTI以及設計復雜性等,才能確保芯片在整個生命周期內的穩定可靠。

評論