加強ESD保護的小竅門

1 引言

如今,從液晶電視到手機等現代電子產品中使用的許多芯片組都是采用遠低于130 nm的先進技術開發的。這些技術對3.3V以上直流電壓的耐受性極低,因此靜電放電脈沖會對此類設備造成災難性的影響。此外,對“板載”或“片載”ESD保護的要求已降至500 V,遠低于8 kV 的典型現場要求。本文介紹了電路板設計人員可以采用的各種技術,以幫助設計人員在所選ESD保護器件無法通過系統ESD 測試時,達到設計所需的ESD 水平。

電路板設計人員不僅需要外部靜電放電保護,還需要考慮到小幾何形狀芯片組的脆弱性,確保其足夠堅固耐用。如前一篇論文所述,在受保護的數據線或I/O 引腳上放置8 kV 額定ESD 器件并不能保證芯片組本身在系統內測試中通過8 kV。

通常情況下,ESD設備本身并不能提供足夠的保護,因此會導致芯片組過早出現故障。本文列舉了一些指導原則,為設計人員加強板載ESD保護提供參考。

2 設備安置和布局

要使ESD保護器發揮最大功效,器件的位置和布局至關重要。為此,設計人員最好了解各種寄生電感對電路板的影響。需要特別關注的是電感,因為僅通過1 nH的8 kV ESD 沖擊(即30 A)就會在PCB 線路上產生30 V 的尖峰電壓:

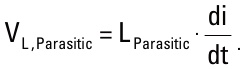

注:本討論假定所有ESD威脅都通過圖1中的端口進入系統。

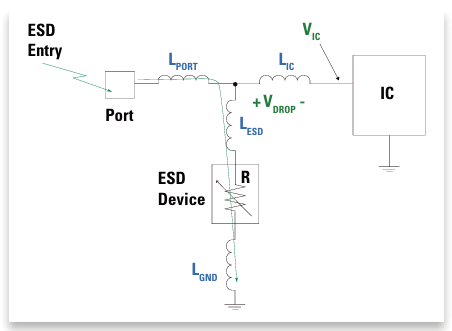

圖1 靜電放電器件需要考慮的四個寄生電感

在決定ESD 器件的位置時,應考慮LESD、LGND、LIC 和LPORT 這四個寄生電感,圖1 顯示了它們的位置。LESD 和LGND 有增加箝位電壓(或VIC)的作用,而LIC和LPORT 則對設計者有利。我們先來看看這兩個有害電感。

3 LESD和LGND

有時,電路板的布局不允許將ESD 器件直接放置在PCB 線路上。原因各有不同,但歸根結底,將靜電放電元件放置在距離受保護數據線一厘米遠的地方,就能迅速轉化為數十伏的電壓。GND 總線也是如此。在某些設計中ESD 器件的GND 必須通過多個通孔,甚至要經過迂回路徑才能到達GND 平面。

除了流經ESD 設備的ESD 電流所產生的電壓外,這兩個電感還會產生電壓尖峰(即IPEAK * RDYNAMIC)。

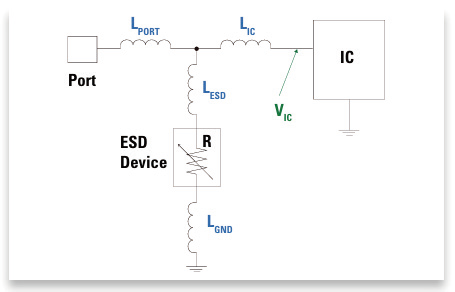

下面的簡化示例將說明LESD 和LGND 對VIC 的影響。在舉例說明之前,我們需要指出的是,常見的PCB 制造工藝可為典型的微帶線跡提供約3 nH/cm(假設具有一定的寬度、厚度和介電常數)。

有鑒于此,讓我們在本例中假設一個8 kV 的ESD脈沖和一個動態電阻為1 Ω的ESD器件。此外,讓我們看看兩種不同的布局,布局A 和布局B,它們的LESD=LGND=1.5 nH(各為0.5 cm)和LESD=LGND=3.0 nH(各為1.0 cm)。

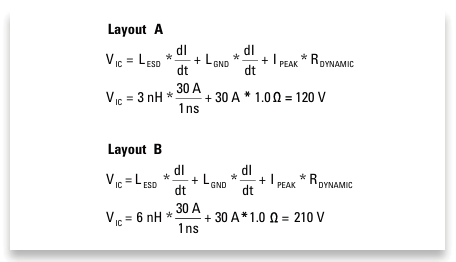

因此,只要將痕量長度(即LESD 和LGND)從0.5 cm增加到1 cm,VIC 就能增加75%。圖2 顯示了布局B 以及與每個元件相關的電壓。

圖2 帶相關電壓的布局B圖示例

4 LIC和LPORT

在許多ESD器件數據表中,通常會說明要將器件盡可能靠近ESD進入點。這樣做的目的是使LPORT 與LIC 的比率盡可能小(即LIC>>LPORT)。LPORT的電感不一定會影響整體ESD性能,但LIC的電感肯定會。

LIC的非線性特性將通過提供“朝向”集成電路的巨大壓降,對ESD 脈沖的初始峰值電流起到緩沖作用。

隨著電感的減小(即ESD器件越來越靠近集成電路),壓降會不斷減小,直至不再產生額外的優勢。因此,對設計人員最有利的是使LPORT與LIC的比率盡可能小,以利用PCB 線路的寄生特性。圖3 顯示了我們所指的電壓降。

圖3 集成電路的電壓降

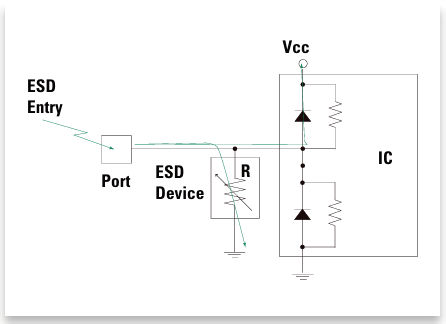

圖4 靜電放電器件和受保護的集成電路分擔靜電放電脈沖的電流負載

利用LIC和LPORT是提高整體ESD性能的直接方法。不過,有些設計無論上述比率多低,都會過早失效。換句話說LIC的值無法為峰值ESD電流提供足夠的緩沖。

5 緩沖電阻

有時,采用前述技術還不足以為特定電路板設計提供最大的ESD 保護。原因是“片上”ESD 結構的電流過大,導致I/O 與GND 或VCC 短路而損壞。

圖4 顯示,ESD 器件和受保護的集成電路實際上分擔了來自ESD脈沖的電流負載,這有助于更清楚地說明問題。該圖(減去跡線電感)顯示的是正靜電放電脈沖,其中保護裝置承擔了大部分電流,但它與集成電路本質上是一個電阻分壓器。(注:圖中顯示集成電路的兩個導軌上有二極管鉗位,但片上保護裝置可以是任何其他靜電放電結構,如可控硅。這樣做的目的是為了說明任何片上ESD結構都有一些與ESD器件并聯的等效電阻)。

如圖4所示,集成電路上的導軌二極管負責將剩余電流或“讓通”電流導入VCC(通常通過旁路電容返回GND)。很難確定集成電路ESD 保護的等效電阻是多少,但毫無疑問,它要比板載ESD 器件高得多。

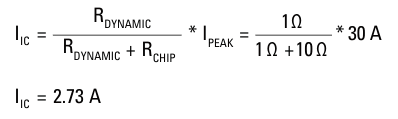

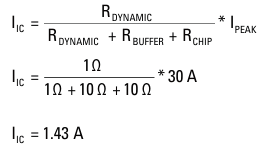

例如,如果片上保護器(RCHIP) 的電阻為10 Ω,外部ESD 保護器的RDYNAMIC為1 Ω,則集成電路的峰值電流將為:

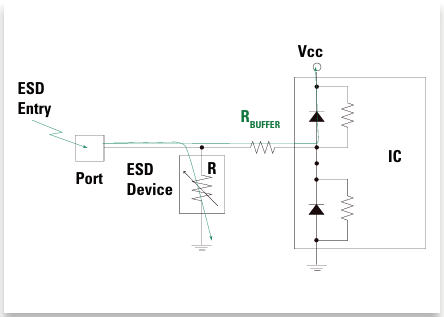

為幫助降低流入集成電路的峰值電流,可在外部靜電放電裝置和集成電路之間串聯電阻,如圖5 所示。

圖5 在外部ESD保護裝置與集成電路(IC)之間串聯顯示電阻

通過增加一個10 Ω 的緩沖電阻,流入集成電路的峰值電流可降低近50%(在本例中)。

顯然,電阻值可以增加到10 Ω 以上,以進一步減小泄放電流,而最大電阻值往往取決于應用的具體情況。

還應注意的是,在HDMI 和USB 3.0 等一些高速應用中使用這種技術時必須格外小心。RBUFFER 電阻會干擾線路阻抗,使信號衰減超出這兩種標準的合規規格,但精心的電路板設計可以彌補任何不良影響。不過,電路板設計人員應在工具箱中保留這項技術,并在電路板或系統內ESD 電平低于要求時加以應用。

6 結束語

如今,現代芯片組比以往任何時候都更容易受到ESD 瞬變的損害。由于采用了小型幾何技術,這些集成電路需要堅固耐用的外部ESD 解決方案,以經受住系統內ESD 測試。

本文給出了電路板設計人員可用于優化ESD 解決方案的四種策略或程序。

● 減少寄生“存根”或LESD 的長度;

● 減少GND 線路的長度和/ 或用于減少LGND 的過孔數量;

● 在給定的設計中使LIC 和LPORT 的比率盡可能小;

● 如果上述1~3 項還不夠,則在ESD 器件和集成電路之間使用緩沖電阻。

所有這些做法都是為了降低集成電路的電壓,并限制芯片上ESD 結構必須處理的電流。遵循這些簡單的規則,電路板設計人員就能獲得更強大的ESD 解決方案,從而超越行業標準。

(本文來源于《EEPW》202507)

評論