Cadence率先推出業(yè)內(nèi)首款LPDDR6/5X 14.4Gbps內(nèi)存IP,為新一代AI基礎(chǔ)架構(gòu)助力

楷登電子(美國 Cadence 公司)近日宣布業(yè)內(nèi)首個 LPDDR6/5X 內(nèi)存 IP 系統(tǒng)解決方案完成流片。該解決方案已經(jīng)過優(yōu)化,運行速率高達(dá) 14.4Gbps,比上一代 LPDDR DRAM 快 50%。全新的 Cadence? LPDDR6/5X 內(nèi)存 IP 系統(tǒng)解決方案是擴(kuò)展 AI 基礎(chǔ)架構(gòu)的關(guān)鍵驅(qū)動因素。經(jīng)過擴(kuò)展之后,AI 基礎(chǔ)架構(gòu)可以適應(yīng)新一代 AI LLM、代理 AI 及其他垂直領(lǐng)域計算密集型工作負(fù)載對于內(nèi)存帶寬和容量的需求。在這方面,Cadence 目前正在與領(lǐng)先的 AI、高性能計算(HPC)和數(shù)據(jù)中心客戶進(jìn)行多項合作。

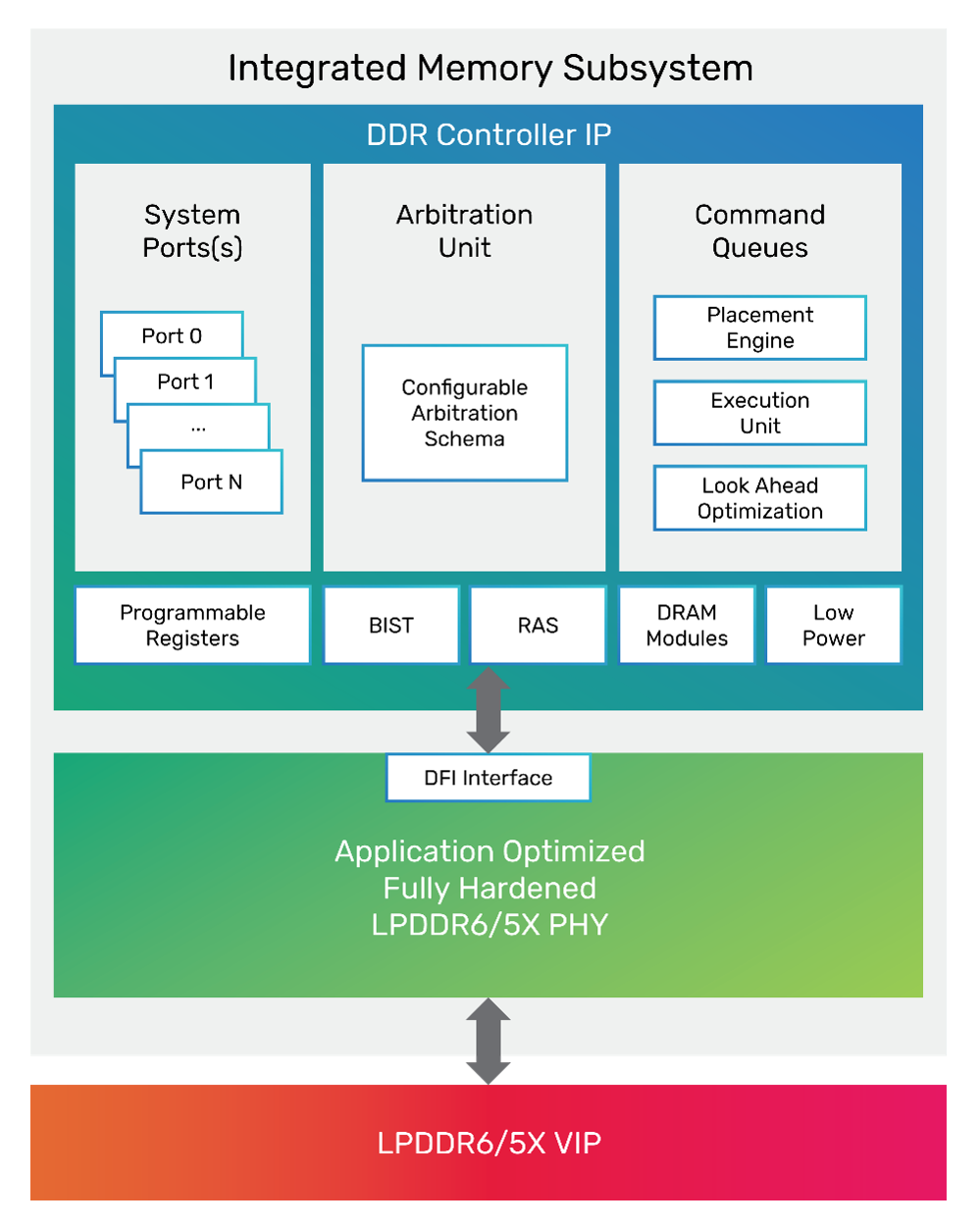

Cadence LPDDR6/5X system solution example

Cadence 滿足 JEDEC LPDDR6/5X 標(biāo)準(zhǔn)的 IP 包括先進(jìn)的 PHY 架構(gòu)和高性能控制器,旨在最大限度地改善功耗、性能和面積(PPA),同時支持 LPDDR6 和 LPDDR5X DRAM 協(xié)議,以實現(xiàn)更高的靈活性。該解決方案利用 Cadence Chiplet 框架,支持原生集成到傳統(tǒng)單片 SoC 和多芯片系統(tǒng)架構(gòu)中,從而實現(xiàn)異構(gòu) Chiplet 集成。包含上一代 LPDDR 的 Chiplet 框架已于 2024 年成功流片。

Cadence 高級副總裁兼芯片解決方案事業(yè)部總經(jīng)理 Boyd Phelps 表示:“數(shù)據(jù)中心從 HPC 計算虛擬化進(jìn)化到大規(guī)模 AI 訓(xùn)練和推理,推動了 AI 基礎(chǔ)架構(gòu)的大規(guī)模建設(shè),在此背景下,必須思考如何通過內(nèi)存接口實現(xiàn)高效的數(shù)據(jù)移動。LPDDR6 已成為加速計算的關(guān)鍵推動因素,可提供高效執(zhí)行 AI 推理所需的速度、帶寬、功耗配置和容量。憑借此次流片,Cadence 將繼續(xù)保持我們在內(nèi)存 IP 領(lǐng)域的卓越地位,提供業(yè)界首款以集成子系統(tǒng)形式交付的 LPDDR6 方案,并針對客戶應(yīng)用進(jìn)行了優(yōu)化。”

完整的 PHY 和控制器內(nèi)存系統(tǒng)采用全新高性能、可擴(kuò)展且適應(yīng)性強(qiáng)的架構(gòu),該架構(gòu)基于 Cadence 久經(jīng)考驗且大獲成功的 DDR5 12.8Gbps、LPDDR5X 10.7Gbps 和 GDDR7-36G 產(chǎn)品線。作為 Cadence 全新 LPDDR6 IP 產(chǎn)品線的首款產(chǎn)品,它支持 LPDDR6 和 LPDDR5X 標(biāo)準(zhǔn),包括 LPDDR5X CAMM2。

此先進(jìn)的 LPDDR6/5X 內(nèi)存 IP 系統(tǒng)解決方案適用于 AI、移動、消費電子、企業(yè) HPC 和云數(shù)據(jù)中心市場,可為具有各種性能、容量和成本目標(biāo)的最終產(chǎn)品提供更大的靈活性,確保長時間的生產(chǎn)運行。LPDDR6/5X PHY 可針對不同的封裝和系統(tǒng)拓?fù)溥M(jìn)行定制,并可作為插入式硬核提供。這能確保快速可靠的集成,也就意味著加快上市速度。

Cadence LPDDR6/5X 控制器包含一套完整的行業(yè)標(biāo)準(zhǔn)和先進(jìn)的內(nèi)存接口功能,例如支持 Arm? AMBA? AXI 總線。內(nèi)存控制器作為 RTL 軟核提供,以便在功能、功耗、面積和性能方面提供更大的靈活性。

Cadence LPDDR6 解決方案包含 LPDDR6 內(nèi)存模型,允許工程師執(zhí)行全面的驗證,并確保系統(tǒng)級芯片(SoC)設(shè)計與最新的 JEDEC 接口標(biāo)準(zhǔn)兼容,幫助他們盡快采用這項新技術(shù)。LPDDR6 內(nèi)存模型包括一套完整的協(xié)議檢查、功能覆蓋和驗證計劃。

新的 LPDDR6/5X IP 是 Cadence 全面的內(nèi)存 IP 系統(tǒng)解決方案系列的最新成員,該系列產(chǎn)品還包括 DDR、GDDR 和 HBM。Cadence 內(nèi)存 IP 采用公司卓越的模擬/混合信號設(shè)計工具進(jìn)行設(shè)計。當(dāng)與 Cadence 基于 UCIe? 的 Chiplet 框架結(jié)合使用時,新的 LPDDR6/5X IP 和 Cadence 其他先進(jìn)的內(nèi)存和接口 IP 可提供一個優(yōu)化的解決方案,支持快速的 Chiplet 實現(xiàn)。

評論