Lattice MXO2: 2位7段數碼管顯示

數碼管顯示

硬件說明

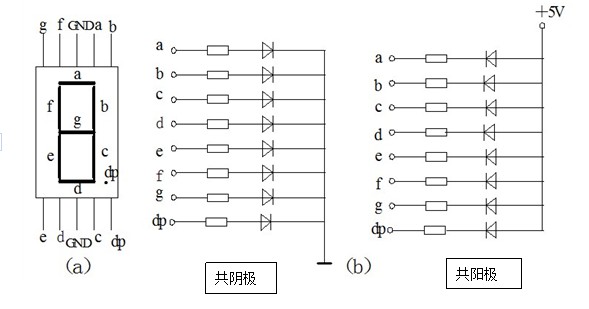

數碼管是工程設計中使用很廣的一種顯示輸出器件。一個7段數碼管(如果包括右下的小點可以認為是8段)分別由a、b、c、d、e、f、g位段和表示小數點的dp位段組成。實際是由8個LED燈組成的,控制每個LED的點亮或熄滅實現數字顯示。通常數碼管分為共陽極數碼管和共陰極數碼管,結構如下圖所示:

圖1 共陽極、共陰極數碼管

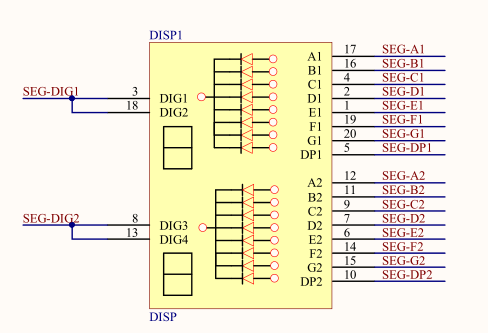

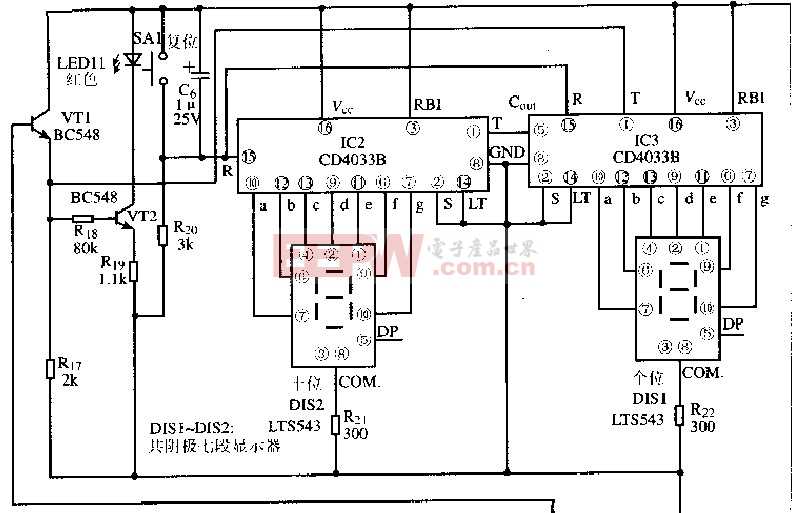

共陰8段數碼管的信號端低電平有效,而共陽端接高電平有效。當共陽端接高電平時只要在各個位段上加上相應的低電平信號就可以使相應的位段發光。比如:要使a段發光,則在a段信號端加上低電平即可。共陰極的數碼管則相反。 可以看到數碼管的控制和LED的控制有相似之處,在小腳丫STEP-MXO2 V2開發板上有兩位共陰極數碼管,

數碼管所有的信號都連接到FPGA的管腳,作為輸出信號控制。FPGA只要輸出這些信號就能夠控制數碼管的那一段LED亮或者滅。這樣我們可以通過開關來控制FPGA的輸出,和3. 3-8譯碼器實驗一樣,通過組合邏輯的輸出來控制數碼管顯示數字,下面是數碼管顯示的表格

這其實是一個4-16譯碼器,如果我們想數碼管能顯示16進制可以全譯碼,如果只想顯示數字,可以只利用其中10個譯碼,下面看看如果用Verilog來實現。

Verilog代碼

// ******************************************************************** // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // ******************************************************************** // File name : segment.v // Module name : segment // Author : STEP // Description : segment initial // Web : www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2017/03/02 |Initial ver // -------------------------------------------------------------------- // Module Function:數碼管的譯碼模塊初始化 module LED (seg_data_1,seg_data_2,seg_led_1,seg_led_2); input [3:0] seg_data_1; //數碼管需要顯示0~9十個數字,所以最少需要4位輸入做譯碼 input [3:0] seg_data_2; //小腳丫上第二個數碼管 output [8:0] seg_led_1; //在小腳丫上控制一個數碼管需要9個信號 MSB~LSB=DIG、DP、G、F、E、D、C、B、A output [8:0] seg_led_2; //在小腳丫上第二個數碼管的控制信號 MSB~LSB=DIG、DP、G、F、E、D、C、B、A reg [8:0] seg [9:0]; //定義了一個reg型的數組變量,相當于一個10*9的存儲器,存儲器一共有10個數,每個數有9位寬 initial //在過程塊中只能給reg型變量賦值,Verilog中有兩種過程塊always和initial //initial和always不同,其中語句只執行一次 begin seg[0] = 9'h3f; //對存儲器中第一個數賦值9'b00_0011_1111,相當于共陰極接地,DP點變低不亮,7段顯示數字 0 seg[1] = 9'h06; //7段顯示數字 1 seg[2] = 9'h5b; //7段顯示數字 2 seg[3] = 9'h4f; //7段顯示數字 3 seg[4] = 9'h66; //7段顯示數字 4 seg[5] = 9'h6d; //7段顯示數字 5 seg[6] = 9'h7d; //7段顯示數字 6 seg[7] = 9'h07; //7段顯示數字 7 seg[8] = 9'h7f; //7段顯示數字 8 seg[9] = 9'h6f; //7段顯示數字 9 end assign seg_led_1 = seg[seg_data_1]; //連續賦值,這樣輸入不同四位數,就能輸出對于譯碼的9位輸出 assign seg_led_2 = seg[seg_data_2]; endmodule

引腳分配

小腳丫上正好有4路按鍵和4路開關,可以用來作為輸入信號分別控制數碼管的輸出。按照下面表格定義輸入輸出信號

| 信號 | 引腳 | 信號 | 引腳 |

|---|---|---|---|

| segdata1(0) | M7 | segdata2(0) | L14 |

| segdata1(1) | M8 | segdata2(1) | M13 |

| segdata1(2) | M9 | segdata2(2) | M14 |

| segdata1(3) | M10 | segdata2(3) | N14 |

| 信號 | 引腳 | 信號 | 引腳 |

|---|---|---|---|

| segled1(0) | A10 | segled2(0) | C12 |

| segled1(1) | C11 | segled2(1) | B14 |

| segled1(2) | F2 | segled2(2) | J1 |

| segled1(3) | E1 | segled2(3) | H1 |

| segled1(4) | E2 | segled2(4) | H2 |

| segled1(5) | A9 | segled2(5) | B12 |

| segled1(6) | B9 | segled2(6) | A11 |

| segled1(7) | F1 | segled2(7) | K1 |

| segled1(8) | C9 | segled2(8) | A12 |

配置好以后編譯下載程序。這樣可以通過按鍵或者開關來控制相應的數碼管顯示數字。如果你想顯示16進制的AbCDeF在數碼管,可以試試修改程序。這時候一定要定義一個16*9的存儲器來初始化。

小結

了解了小腳丫數碼管的工作原理,在下個實驗我們將進行到有趣的時序邏輯。首先是如何控制時鐘分頻。

評論