專為工業應用而設計的MOSFET—TOLT封裝

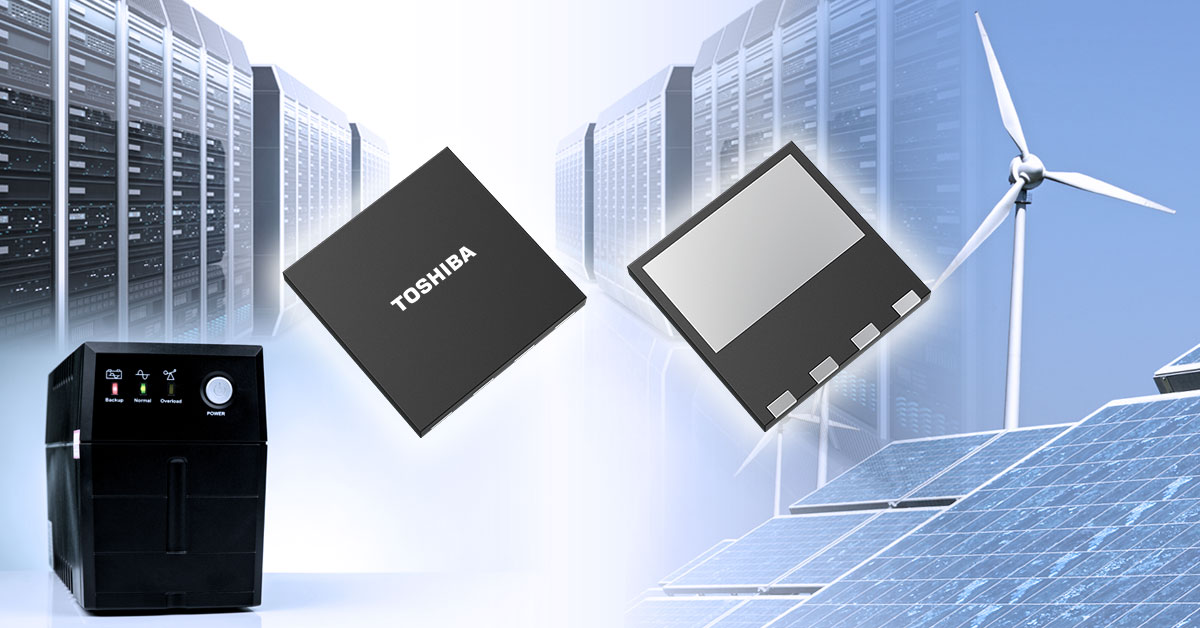

近年來,工業應用對MOSFET 的需求越來越高。從機械解決方案和更苛刻的應用條件都要求半導體制造商開發出新的封裝方案和實施技術改進。從最初的通孔封裝(插件)到 DPAK 或 D2PAK 等表面貼裝器件 (SMD),再到最新的無引腳封裝,以及內部硅技術的顯著改進,MOSFET 解決方案正在不斷發展,以更好地滿足工業市場新的要求。本文介紹了 TOLT 的封裝方案、熱性能和電路板的可靠性。

本文引用地址:http://www.czjhyjcfj.com/article/202212/441145.htm關鍵特性,主要優勢和應用

目標應用市場

英飛凌公司的 TOLT(JEDEC:HDSOP-16),封裝OptiMOS? 5 功率 MOSFET,有助于實現非常高的功率水平。由于通過頂部冷卻改善了熱阻,TOLT 可以在不增加器件數量和系統尺寸的情況下滿足功率要求高的應用需求。因此,TOLT 封裝的重點應用是大電流應用。該封裝適用于功率水平高達 50 kW 的大功率電機驅動器,具體應用如下:

圖1 具體應用

封裝設計

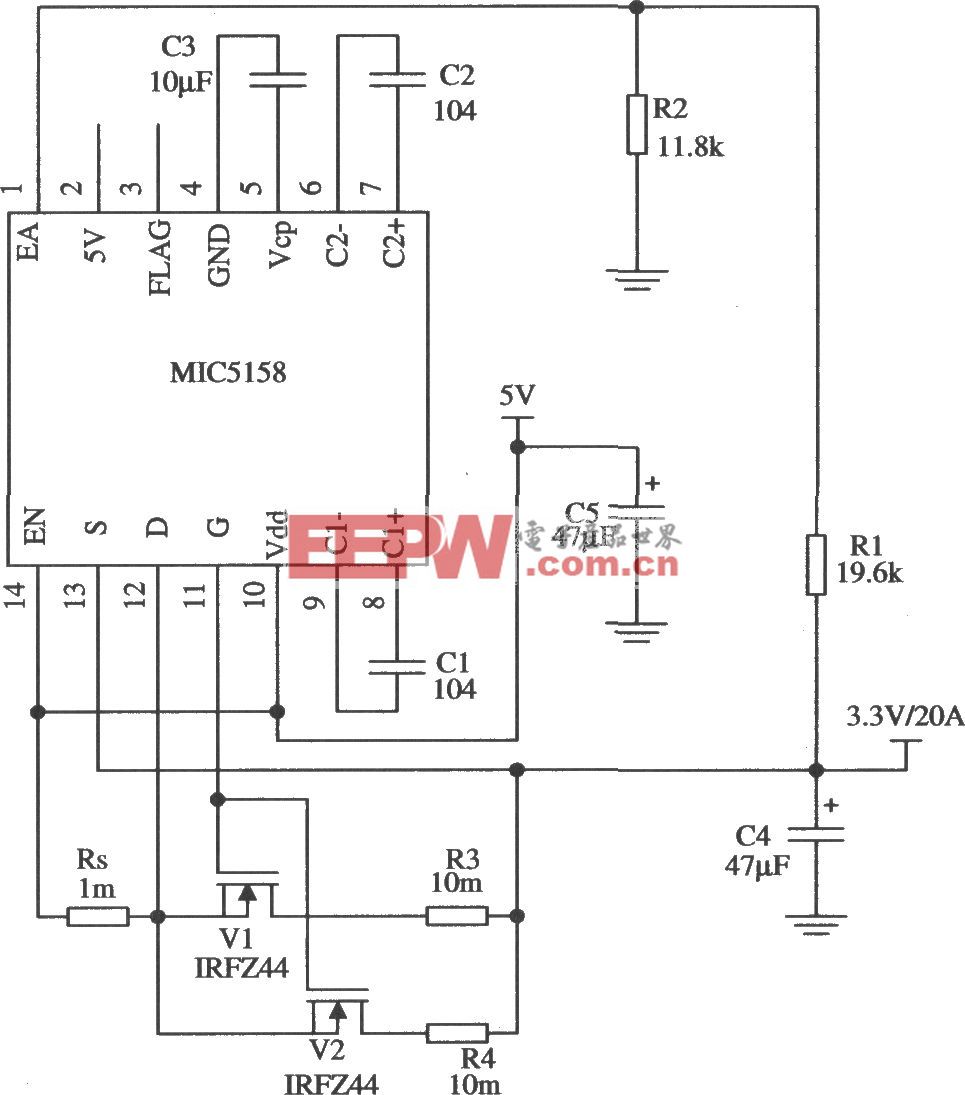

新 TOLT 封裝的概念不同于標準的底部散熱功率 MOSFET。在 TOLT 中,封裝內的引線框架倒置,漏極焊盤(芯片底部 = 漏極連接)暴露在封裝頂部。圖2 為帶有倒置引線框架的封裝的側視圖。

圖2 TOLT 側視圖

封裝外形

圖3 和圖4 為柵極、源極和漏極引腳。一排八個引腳連接到頂部的裸露焊盤,以與電路板進行漏極連接。在封裝的另一側,一個引腳用于柵極控制,其余七個引腳連接到電流源極。

圖3 TOLT 3D 視圖

圖4 TOLT 底視圖

圖5為 TOLT 封裝尺寸細節。兩個方向的高度容差都保持在±0.05 mm。負引腳本體高差的容差為 0.01 至 0.16 mm。

圖5 尺寸圖

TOLT優勢和準則

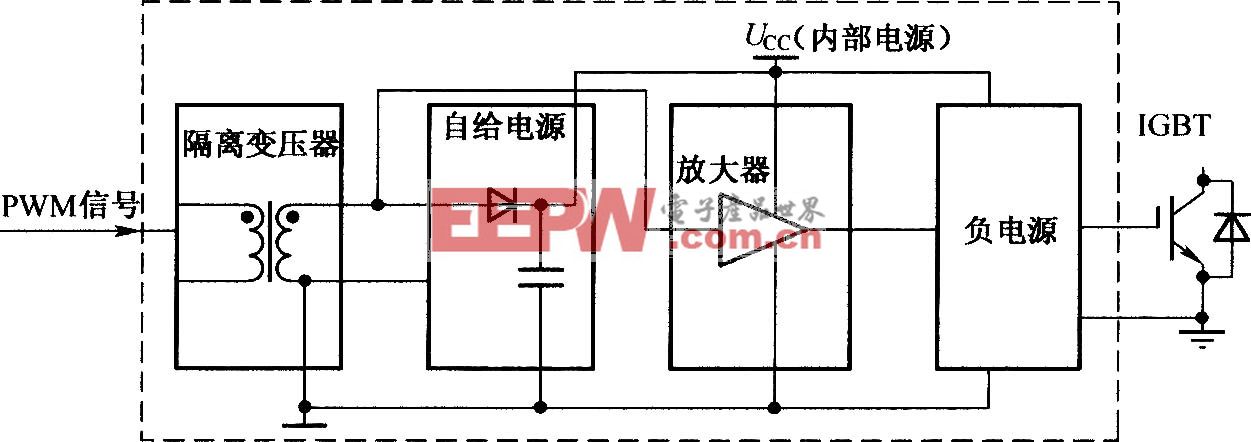

頂部散熱不僅可以獲得更高的應用功率,而且還有其他幾個重要優勢。在標準散熱方案中(圖6),散熱器通常安裝在 PCB 下方。從芯片到外部的熱傳遞路徑如下:這種解決方案的缺點是熱性能降低,具體取決于 PCB 和 TIM/導熱膏參數。這些組件的導熱性差可能會導致過熱和應用功率降低,還可能意味著需要更高的散熱成本。此外,組裝板需要承受更高的溫度,這就需要使用更昂貴的 PCB。

圖6 背面散熱方式中的熱路徑

而得益于頂部散熱方案(圖7),熱路徑可以顯著縮短:通過消除熱路徑中的 PCB 和焊料互連來減少熱路徑對 MOSFET 性能有巨大的影響。

圖7 頂部散熱方式中的熱路徑

英飛凌研究了這兩種解決方案比較:

1.依托頂部散熱設計,漏極暴露在封裝表面,顯著降低管芯和散熱器之間的熱阻,可將 95% 的熱量通過散熱器傳遞,只有5%通過PCB傳遞(圖8),諸如 TOLL 或 D2PAK 等底部散熱型封裝(圖9),其熱量均通過 PCB 傳導至散熱片,從而會導致功率損耗較高。

圖8

圖9

2.SMD組件可以放置在PCB底部的TOLT MOSFET下方(圖10),以優化可用面積;

圖10 TOLL & TOLT 散熱示意圖

3.TOLT增加電流/功率處理能力,相較于 TOLL 封裝,TOLT 封裝的 RthJA 降低了 20%,RthJC 改善近 50%, Rth(J-heatsink) 降低了36% (圖11)。

圖11

4.額外優勢

除了可以為散熱系統實現更高的功率密度或節省成本外,TOLT 產品還有其他優勢。以下是一些示例:

● 由于散熱器沒有安裝在 PCB 下方,也沒有熱量通過 MOSFET 底側傳遞到電路板,因此柵極驅動器或電容可以放在 PCB 的另一側。這樣的解決方案能夠更有效地利用 PCB 空間。

● 增加爬電距離(源極和漏極電勢之間的距離)。

● 可以使用具有較低玻璃化轉變溫度的 PCB。

● 傳遞到 PCB 和附近組件中的熱量更少。

5.熱界面材料厚度

為保證 TOLT 封裝的最佳熱性能,并保證封裝盡可能低的熱阻,優化 TIM 厚度就顯得至關重要。英飛凌為 TOLT 封裝模擬了幾種不同 TIM 厚度的情況(圖12),從而分析其對從結到散熱片總 RTH 的影響。在模擬中,散熱片溫度固定為 85°C 的環境溫度。

圖12 為 Rth 對于不同 TIM 厚度的 TIM 熱導率的相關性

從圖中可以看出,TIM 越薄,熱阻越低。但是,應注意 TIM 的熱導率 (λ) 值。更好的熱導率補償了 TIM 厚度的負面影響。

市場上現有的 TIM 的熱導率通常在 3 到 6 W/mK 之間。為了達到最佳的熱性能和足夠的電隔離相平衡,系統工程師應優化 TIM 的厚度和熱參數。下表為一些目前市場上現有的 TIM 示例。

客戶最常用且在市場上廣泛使用的材料是熱導率在 3 至 4 W/mK 范圍內的 TIM。根據對該值的仿真,MOSFET 結和散熱片之間的熱阻在 0.8 和 3K/W 之間變化,具體取決于 TIM 厚度。實際 TIM 厚度為 300 至 500 μm 時,熱阻值可達 1.5 至 2.4K/W。當 Rth 等于 2.4 K/W 且 MOSFET 結與外殼之間的溫差為 90°C(假設 Tcase = 85°C 和 Tjmax = 175°C)時,單個 TOLT MOSFET 可消耗大約 40 W 的功率。

6.電參數

TOLT 封裝中的 MOSFET 具有與相應 TOLL 部件相同的 RDS(on) 值。例如,采用 TOLT 封裝的出色的100V MOSFET(IPTC015N10NM5) 和相應的TOLL(IPT015N10N5),RDS(on),max 均為 1.5 mΩ。

參數比較:TOLL vs. TOLT

與 TOLL 相比,在帶過孔的普通 2s2p 電路板和 85°C 的環境溫度條件下,TOLT 的最大改進之處在于結到散熱片的熱阻 Rth 明顯降低。Rth 降低了近 50%,這會導致總耗散功率提高 90% 以上。

TOLT的電路板可靠性

所有 SMD MOSFET 的另一個重要方面是不同應用條件下的電路板的可靠性。在苛刻的工業應用中使用這些 MOSFET 會使部件承受巨大的機械應力。用于評估 PCB 上封裝可靠性的最常見測試是板上溫度循環 (TCoB) 測試。TOLT 封裝的散熱片安裝在封裝頂部,因此還必須研究該部件可以承受的最大機械應力。

1. 板載溫度循環可靠性

電子元件在工作期間會暴露在不斷變化的溫度下,這會導致材料膨脹。每種材料都有其自身的熱膨脹系數,如果應力足夠大,熱膨脹率的差異可能會導致焊點出現裂紋。證明對熱機械應力的魯棒性的測試就是 TCoB 測試。IPC-9701 標準確定了應該如何以及在何種條件下進行 TCoB 測試。

圖13 IPC-9701:表面貼裝焊接部件的性能測試方法和驗證要求

圖14 為汽車應用中零部件的測試條件

從圖13 和圖14 中可以看出,汽車零件應能 -45°C 至 +125°C 下承受 1,000 次循環,期間無故障出現。盡管通過了工業驗證,英飛凌 MOSFET 仍根據更嚴格的汽車標準進行了測試。根據標準要求,升溫速率應小于每分鐘 20°C。然而,在英飛凌的 TCoB 測試期間,升溫速率條件為每分鐘 60°C。這會增加器件上的應力,還能滿足更嚴格的熱沖擊測試要求。這種嚴苛的測試條件使英飛凌的封裝承受了比 IPC-9701 標準要求更大的應力,從而證明了其卓越的魯棒性和電路板級可靠性。

在英飛凌進行的 TCoB 測試期間,TOLT 部件受到監控,電氣故障的標準是電阻增加 20%。圖15測試結果表明,TOLT 封裝可以承受至少 6,000 次循環而不會出現電氣故障。6,000 次循環后,測試結束。

圖15 TOLT 在 TCoB 測試中達到至少 6,000 次循環

熱仿真

本節將介紹和討論不同電路板和散熱片安裝配置的熱仿真結果。在圖表中可以看到各種配置的熱阻抗值。

在兩種不同的散熱系統結構下,仿真了從結到環境的熱阻:

a) 在固定環境溫度下,通過頂部散熱的 Rth_JD1 (圖16),以及通過頂部散熱,同時讓散熱片保持自然對流的 Rth_JD2 (圖17)。

b) 在固定環境溫度下,通過 PCB 和頂部散熱 的Rth_JH1D1 (圖18),以及在自然熱對流下,通過 PCB 和頂部散熱的 Rth_JH2D2 (圖19) 。

對于每種散熱方式,仿真了四種不同的 PCB 配置:2s2p(四層 PCB,銅厚 1 oz. – 2 oz. – 2 oz. – 1 oz. ), 帶和不帶過孔,以及 1s0p(單層 PCB,銅厚 1 oz. ),帶和不帶過孔。所選 TIM 的熱導率為 0.7 W/mK,厚度為 100 μm。在相關情況下,環境溫度設置為 85°C。

如圖16所示,對于頂部散熱,在熱量直接傳遞到主動冷卻的散熱片(溫度固定)時,PCB 的選擇在 Zth 性能方面沒有顯著差異。這意味著可以使用玻璃化轉變溫度較低的更經濟的電路板。無論使用哪種電路板, 熱阻抗值都約為 2.8 K/W。

圖16 不同電路板的 TOLT 熱阻抗;頂部散熱溫度固定為 Tambient

圖17 不同電路板的 TOLT 熱阻抗;自由熱對流

但在自由熱對流 (圖17) 的情況下,電路板的選擇可能會有所不同,因為一些熱量會傳遞到 PCB。普通 2s2p 電路板的熱阻將增加到 19.5 K/W。

此外,仿真結果表明,如果在 PCB 下方安裝第二個散熱片,熱性能不會顯著提高。例如,沒有過孔的 2s2p 電路板,其封裝上方只有一個散熱片,而 PCB 下方沒有散熱片,電路板熱阻抗為 2.77 K/W。如果在電路板下方增加一個散熱片,熱阻抗僅略微降低到 2.59 K/W,這可以忽略不計。圖18和圖19為兩側均帶有散熱片的仿真結果。

圖18 不同電路板的 TOLT 熱阻抗;頂部散熱溫度固定為 Tambient

圖19 不同電路板的 TOLT 熱阻抗;自由熱對流

總結

新型頂部散熱 TOLT 封裝,為大功率工業應用在 FR4 PCB 上實現。TOLT 由于縮短了從管芯結到散熱片的熱路徑,因此改善了熱阻,從而提高了電氣性能。

為了確保最佳熱性能,在開發 TOLT 封裝過程中,英飛凌設計人員采取了不同的措施。這些措施包括最小化封裝高度,引入引腳的負引腳本體高差,并采用無錫散熱焊盤。影響 TOLT 產品整體熱性能的一個關鍵方面是封裝頂部和散熱片之間的熱界面材料 (TIM)。設計人員可以在 TIM 的厚度、熱導率和價格之間權衡,從而實現預期的熱性能。熱仿真證實,與在 FR4 PCB 上的標準底部散熱解決方案相比,封裝的熱阻有了顯著改善。除了仿真外,還進行了可靠性試驗,例如板上溫度循環、彎曲和壓縮測試。實驗結果證明,TOLT 封裝在頂部有額外負載壓力的情況下可以承受足夠數量的熱沖擊循環,這超過了通用標準的要求。

來源:Arrow

評論