一種應用于折疊/插值型ADC的高速寬帶采樣保持電路

近20 年來,隨著數字通信的快速發展,處于信號鏈路中的模數轉換器(ADC)的作用就越來越重要。其中超高速寬帶ADC 可廣泛應用于衛星、雷達、電子戰、數字示波器、通信等接收機領域[1,2]。傳統高速8位ADC 一般采用全并行結構,盡管該結構轉換速度快,但電路規模隨分辨率n 呈2n 指數增長[3,4],且功耗大。折疊/ 插值型結構ADC 利用折疊與插值轉換關系,可大大減少并行比較器數量,同時轉換速率與全并行結構相當。但是,即使采用雙極工藝,折疊結構電路依然受器件失配影響很大,幸運的是可以采用前端數字校準算法來降低器件失配對電路性能的影響。

本文引用地址:http://www.czjhyjcfj.com/article/202205/434595.htm折疊/ 插值型ADC 的器件失配可以用前端數字校準算法進行修正,但要校準動態的時鐘抖動誤差則需付出極大代價。因此,折疊/ 插值型ADC 的前端一般采用高速寬帶采樣保持電路(S/H),可以有效降低采樣時鐘抖動影響。本文提出的一種基于0.18 μm BiCMOS工藝設計的開環采樣保持電路,采用簡易的數字校準算法即可大大降低電路的增益誤差與失調誤差。電路仿真與實際測試表明,通過數字校準采樣保持電路增益與失調誤差后,ADC 的動態性能可提升10 dB 以上。

1 采樣保持電路設計

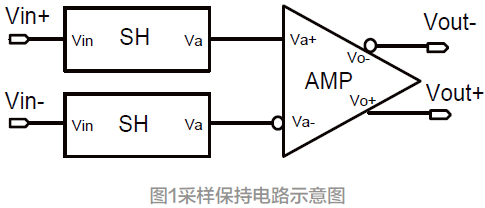

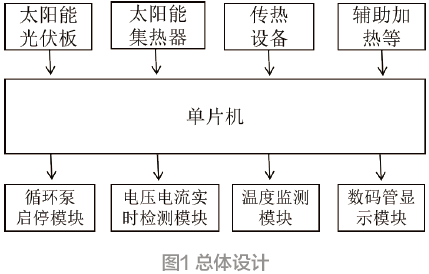

采樣保持電路的采樣率達到2GSPS,所以S/H 電路采用開環結構。如圖1 所示,S/H 電路系統由采樣保持級(SH)電路和放大與驅動級(AMP)電路組成。

在SH 級,電路采用偽差分結構,然后在AMP 級中轉換成差分信號來提高抗干擾能力。模擬輸入信號Vin 被采集并保持,由于SH 級電路采用開環結構以及電路帶寬影響,SH 級電路的放大倍數小于“1”。AMP級電路對SH 級輸出的保持信號進行放大,使S/H 電路系統的信號放大倍數剛好為“1”。此外,AMP 級電路不僅具有強大的驅動后級較大規模折疊電路的能力,還起到消除后級電路對采樣保持轉換時帶來的饋通效應,提升S/H 電路采樣轉換時的線性度。

2 SH級電路設計

為了消除SH 級電路輸入對管電流隨輸入信號變化帶來的影響,本設計中輸入管采用PMOS管代替雙極管。SH 級電路如圖2 所示。由于電路的采樣率高達2GSPS,所以采用開環結構,盡可能提高電路轉換速度。在SH級輸出端加入一個幾十歐姆小電阻,用來調整采樣/ 保持轉換過程中建立信號的過沖效應,以便獲得最快轉換速度。SH 級電路的帶寬BW 如式(1)所示。

式(1)中,RL是SH級電路輸出端電阻,CL是SH級電路輸出端電容。為了保證模擬輸入頻率高達2.5 GHz時,電路的無雜散動態范圍(SFDR)超過65 dB,則保持電容值必須小于0.8 pF。采用小保持電容值可以提升采樣保持電路帶寬,同時會降低采樣相時SH 級電路的線性度。但是,保持相時要提升電路線性度則需要加大采樣保持電容值。此外,增加保持電容值可以減小采樣轉換時對保持電壓的干擾。綜合考慮[5],采樣保持電容值選擇0.5 pF。

3 AMP級電路設計

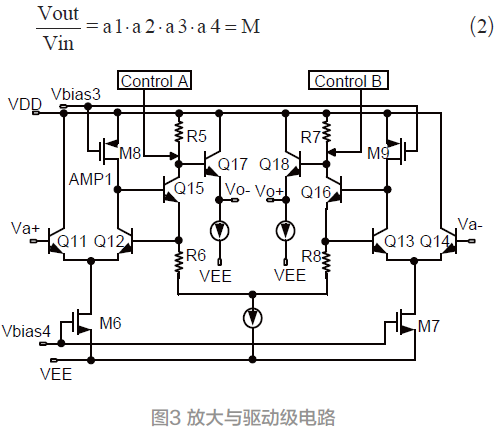

放大驅動級電路的作用是把SH 級輸出的偽差分信號變化真正的差分信號,并驅動后級折疊轉換電路。AMP 級采用一個簡單的開環放大器,如圖3 所示。SH級電路的增益為a1;放大器單元由Q11,Q12,M6 andM8 組成,其增益為a2;用于調整增益的電阻R5 與R6之間比值(R5/R6)為a3;輸出管Q17 與Q18 的增益為a4。那么整個采樣保持電路的增益如式(2)表達:

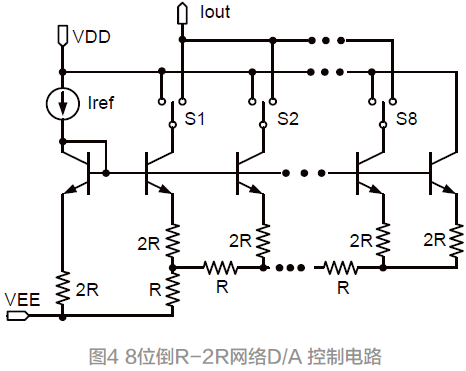

在a1,a2,a4 隨工藝及環境偏差而變化的情況下,可以通過調節R5/R6 的比值,使采樣保持電路的增益剛好為1。在Q17 與Q18 的基極處加入數字控制電路control A 與control B(control A 與control B 相同),分別調節流過電阻R5 與R7 的電流。數字控制電路如圖4 所表,采用8 位倒R-2R 網絡D/A 結構。采樣保持電路輸出電壓由R5? Iout (R7 = R5) 進行調節失調電壓。當采樣保持電路的增益小于“1”時,同時調節controlA 與control B,并使流過電阻R5 與R7 的電流減小,直到整個ADC 系統剛好達到滿度為止,此調節動作都是在系統自校正過程中完成;反之亦然。

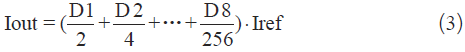

在圖4 中,最大權重數字碼D1 控制開關S1。如果D1 為“1”,S1 右開關導通;如果D1 為“0”,S1 左開關導通。同樣地,D2 控制S2,D3 控制S3……D8 控制S8。通過DAC網絡控制流過R5的電流表達式如式(3)所示:

4 版圖設計與電路測試

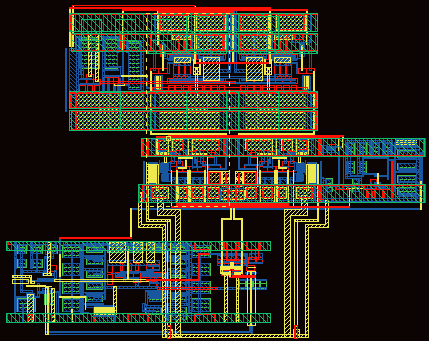

設計的采樣保持電路的版圖如圖5 所示。

圖5 S/H電路版圖

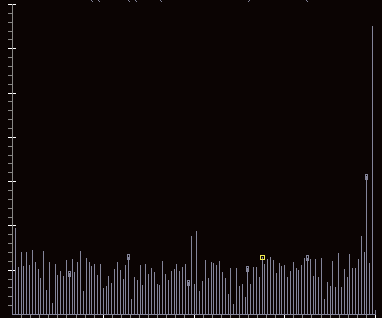

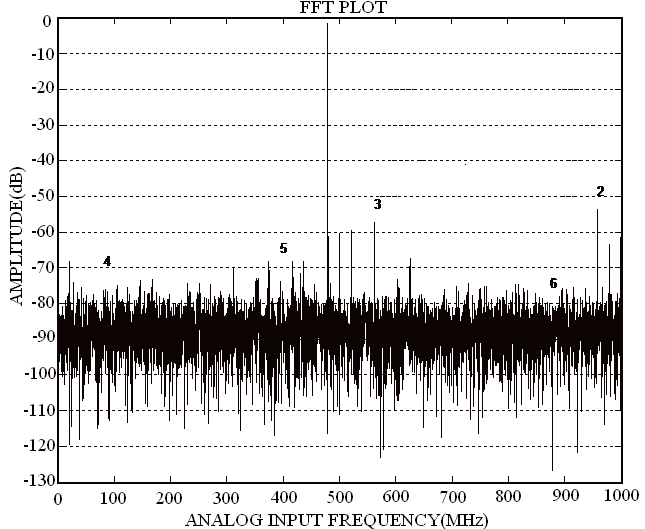

在模擬信號輸入頻率992 MHz、輸入幅度500 mVpp,采樣率2GSPS 條件下對版圖進行后仿真,后仿結果如圖6 所示,SFDR 為65 dB,滿足ADC 設計要求。

圖6 S/H電路版圖后仿結果

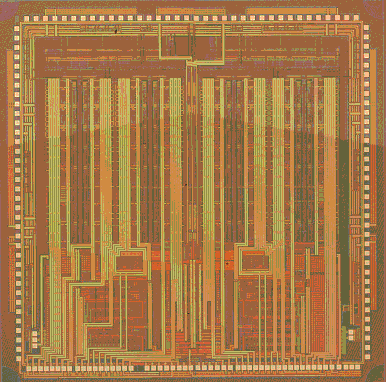

基于0.18 μm BiCMOS 工藝設計的高速寬帶采樣保持電路應用于8 位高速ADC 中,ADC 版圖面積5.256 mm×5.168 mm,如圖7 所示。

圖7 8位ADC照片圖

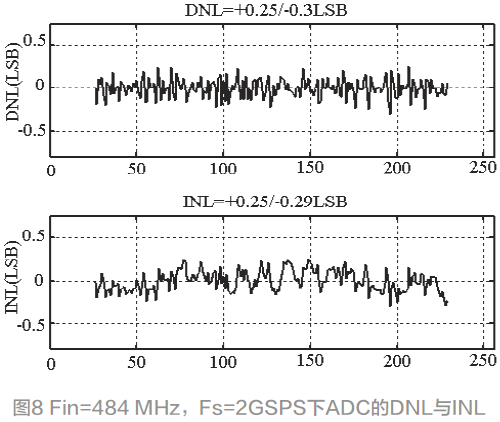

8 位高速ADC 的模擬輸入帶寬超過2 GHz, 在2GSPS 采樣率、50 MHz 模擬輸入頻率下,如采樣保持電路不采用數字校準,則ADC 的有效位只有6 位;如采用數字校準,ADC 的有效位可提升到7.4 位。在2GSPS 采樣率、484MHz 模擬輸入頻率下,啟動數字校準,ADC 實測微分非線性DNL ≤ ±0.3LSB、積分非線性INL ≤ ±0.3LSB,如圖8 所示。ADC 的SFDR 達到52 dB,如圖9 所;有效位為7.32 位。

圖9 Fin=484MHz, Fs=2GSPS下ADC的SFDR

5 結論

本文提出的基于0.18 μm BiCMOS 工藝設計的高速寬帶采樣保持電路,成功應用于8 位高速折疊/ 插值ADC 中,大大提升了ADC 的動態性能與輸入帶寬。該采樣保持電路用開環結構,工作轉換速率超過2GSPS,利用增益與失調數字校準算法提升電路的靜態和動態性能。ADC 電路測試結果優異,表明設計的高速寬帶采樣保持電路滿足要求。

參考文獻:

[1] YU J S, ZHANG R T,ZHANG Z P,et al.A digital calibration technique for an ultra high-speed wide-bandwidth folding and interpolating analog-to-digital converter in 0.18-μm CMOS technology[J]. Journal of Semiconductors,2011,32(1):977.

[2] FLYNN M P,SHEAHAN B.A 400-Msample/s,6-b CMOS Folding and Interpolating ADC[J].IEEE Journal of Solid- State Circuit,1998,33(12):1932.

[3] LEE D, SONG J,SHIN J,et al.Design of a 1.8V 8-bit 500MSPS Folding-Interpolation CMOS A/D Converter with a Folder Averaging Technique[C].18th European Conference on Circuit Theory Design,2007:356.

[4] ALI A M, MORGAN A,DILLON C,et al.A 16 b 250MS/s IF-sampling pipelined A/D converter with background calibration[C].IEEE International Solid-State Circuit Conference Digest of Technical Papers,2010:292.

[5] CHU M, JACOB P,KIM J-W,LeRoy M R,et al.A 40Gs/s Time Interleaved ADC Using SiGe BiCMOS Technology[J]. IEEE Jouurnal of Solid-State Circuit,2010,45(2):380.

(本文來源于《電子產品世界》雜志2022年5月期)

評論