詳解FPGA芯片結構以及開發流程

1.FPGA概述

本文引用地址:http://www.czjhyjcfj.com/article/201808/386159.htmFPGA是英文FieldProgrammableGateArray的縮寫,即現場可編程門陣列,它是在PAL、GAL、EPLD等可編程器件的基礎上進一步發展的產物。它是作為專用集成電路(ASIC)領域中的一種半定制電路而出現的,既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點

2.FPGA芯片結構

FPGA芯片主要由三部分組成,分別是IOE(inputoutputelement,輸入輸出單元)、LAB(logicarrayblock,邏輯陣列塊,對于Xilinx稱之為可配置邏輯塊CLB)和Interconnect(內部連接線)。

2.1 IOE

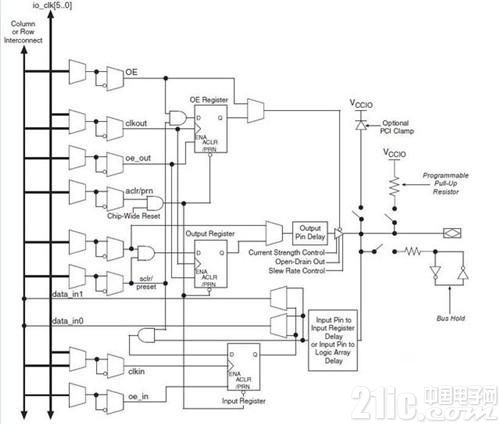

IOE是芯片與外部電路的物理接口,主要完成不同電氣特性下輸入/輸出信號的驅動與匹配要求,比如從基本的LVTTL/LVCMOS接口到PCI/LVDS/RSDS甚至各種各樣的差分接口,從5V兼容到3.3V/2.5V/1.8V/1.5V的電平接口,下面是ALTERA公司的CycloneIVEP4CE115F29設備的IOE結構

EP4CE115F29設備的IOE結構圖

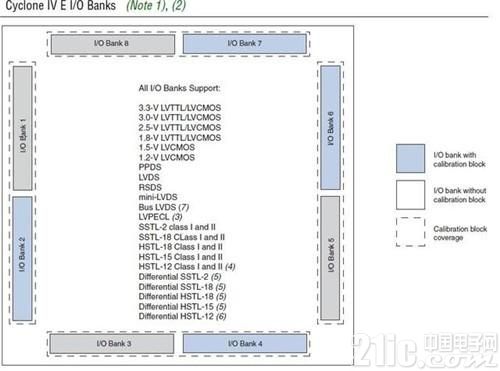

FPGA的IOE按組分類,每組都能夠獨立地支持不同的I/O標準,通過軟件的靈活配置,可匹配不同的電器標準與IO物理特性,而且可以調整驅動電流的大小,可以改變上/下拉電阻,CycloneIV設備有8個IOblank(組),見下圖:

CycloneIV設備的IO組

2.2 LAB

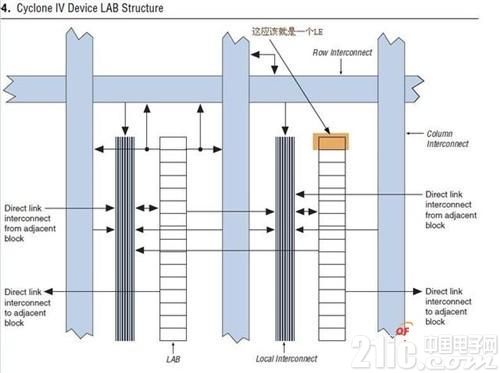

LAB是FPGA的基本邏輯單元,其實際的數量和特性依據所采用的器件的不同而不同,EP4CE115F29設備的每個LAB的布局包括16個LE、LAB控制信號、LEcarrychains、Registerchains和Localinterconnect,其LAB結構圖如下:

LAB結構圖

LE是CycloneIV設備最小的邏輯單元,每個LE主要有LUT和寄存器組成的,

LE的結構圖

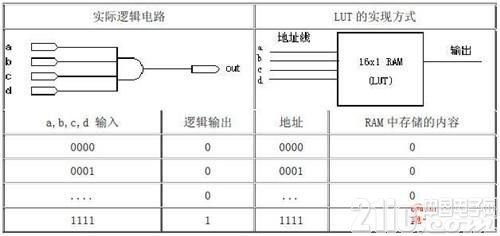

查找表LUT(Look-Up-Table)其本質是一個靜態存儲器SRAM,目前FPGA多采用4輸入的LUT,每個LUT可以看作一個有4位地址線的16x1的RAM。當我們通過原理圖或HDL語言描述了一個邏輯電路后,FPGA開發軟件會自動計算邏輯電路的所有可能的結果,并把結果事先寫入RAM。這樣,在FPGA工作時,每輸入一個信號進行邏輯運算就等于輸入一個地址進行查表,找出地址對應的內容,然后輸出。

LUT的實現原理圖

評論