詳解底層內嵌功能單元與軟核、硬核以及固核

6、底層內嵌功能單元

本文引用地址:http://www.czjhyjcfj.com/article/201808/385260.htm內嵌功能模塊主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP 等軟處理核(Soft Core)。現在越來越豐富的內嵌功能單元,使得單片FPGA 成為了系統(tǒng)級的設計工具,使其具備了軟硬件聯(lián)合設計的能力,逐步向SOC 平臺過渡。

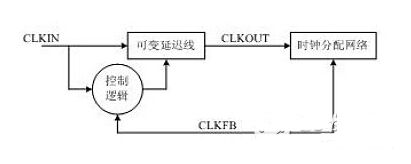

DLL 和PLL 具有類似的功能,可以完成時鐘高精度、低抖動的倍頻和分頻,以及占空比調整和移相等功能。賽靈思公司生產的芯片上集成了DCM 和DLL,Altera 公司的芯片集成了PLL,LatTIce 公司的新型芯片上同時集成了PLL 和DLL。PLL 和DLL 可以通過IP 核生成的工具方便地進行管理和配置。DLL 的結構如圖2-8 所示。

圖2-9 典型的DLL模塊示意圖

7. 內嵌專用硬核

內嵌專用硬核是相對底層嵌入的軟核而言的,指FPGA 處理能力強大的硬核(Hard Core),等效于ASIC 電路。為了提高FPGA 性能,芯片生產商在芯片內部集成了一些專用的硬核。例如:為了提高FPGA 的乘法速度,主流的FPGA 中都集成了專用乘法器;為了適用通信總線與接口標準,很多高端的FPGA 內部都集成了串并收發(fā)器(SERDES),可以達到數十Gbps 的收發(fā)速度。

賽靈思公司的高端產品不僅集成了Power PC 系列CPU,還內嵌了DSP Core 模塊,其相應的系統(tǒng)級設計工具是EDK 和Platform Studio,并依此提出了片上系統(tǒng)(System on Chip) 的概念。通過PowerPC?、Miroblaze、Picoblaze 等平臺,能夠開發(fā)標準的DSP 處理器及其相關應用,達到SOC 的開發(fā)目的。

此外,新推出賽靈思的FPGA 系列如Virtex-5 LXT 還內建了PCI Express 和三態(tài)以太網MAC 硬核(TEMAC),與軟核實現方式相比,硬核可以把功耗降低5~10 倍, 節(jié)約將近90% 的邏輯資源。

Xilinx 三態(tài)以太網MAC 核是一個可參數化的核,非常適合在網絡設備中使用, 例如開關和路由器等。可定制的TEMAC 核使系統(tǒng)設計者能夠實現寬范圍的集成式以太網設計,從低成本10/100 以太網到性能更高的1GB端口。TEMAC 核設計符合 IEEE 802.3 規(guī)范的要求,并且可以在 1000Mbps、100 Mbps 和 10 Mbps 模式下運行。

另外,它還支持半雙工和全雙工操作。TEMAC 核通過 Xilinx CORE Generator? 工具提供,是 Xilinx 全套以太

網解決方案的一部分。

2.1.3 軟核、硬核以及固核的概念

IP(Intelligent Property) 核是具有知識產權核的集成電路芯核總稱,是經過反復驗證過的、具有特定功能的宏模塊,與芯片制造工藝無關,可以移植到不同的半導體工藝中。到了SOC 階段,IP 核設計已成為ASIC 電路設計公司和FPGA 提供商的重要任務,也是其實力體現。對于FPGA 開發(fā)軟件,其提供的IP 核越豐富,用戶的設計就越方便,其市場占用率就越高。目前,IP 核已經變成系統(tǒng)設計的基本單元,并作為獨立設計成果被交換、轉讓和銷售。

從IP核的提供方式上,通常將其分為軟核、固核和硬核這3類。從完成IP核所花費的成本來講,硬核代價最大;從使用靈活性來講,軟核的可復用使用性最高。

1. 軟核(Soft IP Core)

軟核在EDA 設計領域指的是綜合之前的寄存器傳輸級(RTL) 模型;具體在FPGA 設計中指的是對電路的硬件語言描述,包括邏輯描述、網表和幫助文檔等。軟核只經過功能仿真,需要經過綜合以及布局布線才能使用。其優(yōu)點是靈活性高、可移植性強,允許用戶自配置;缺點是對模塊的預測性較低,在后續(xù)設計中存在發(fā)生錯誤的可能性,有一定的設計風險。軟核是IP 核應用最廣泛的形式。

2. 固核(Firm IP Core)

固核在EDA 設計領域指的是帶有平面規(guī)劃信息的網表;具體在FPGA 設計中可以看做帶有布局規(guī)劃的軟核,通常以RTL 代碼和對應具體工藝網表的混合形式提供。將RTL 描述結合具體標準單元庫進行綜合優(yōu)化設計,形成門級網表,再通過布局布線工具即可使用。和軟核相比,固核的設計靈活性稍差,但在可靠性上有較大提高。目前,固核也是IP 核的主流形式之一。

3. 硬核 (Hard IP Core)

硬核在EDA 設計領域指經過驗證的設計版圖;具體在FPGA 設計中指布局和工藝固定、經過前端和后端驗證的設計,設計人員不能對其修改。不能修改的原因有兩個:首先是系統(tǒng)設計對各個模塊的時序要求很嚴格,不允許打亂已有的物理版圖;其次是保護知識產權的要求,不允許設計人員對其有任何改動。IP 硬核的不許修改特點使其復用有一定的困難,因此只能用于某些特定應用,使用范圍較窄。

評論