DDRx的關鍵技術介紹

ODT(On-Die Termination,片內終結)

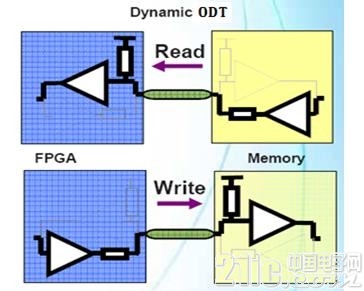

ODT也是DDR2相對于DDR1的關鍵技術突破,所謂的終結(端接),就是讓信號被電路的終端吸收掉,而不會在電路上形成反射,造成對后面信號的影響。顧名思義,ODT就是將端接電阻移植到了芯片內部,主板上不再有端接電路。在進入DDR時代,DDR內存對工作環境提出更高的要求,如果先前發出的信號不能被電路終端完全吸收掉而在電路上形成反射現象,就會對后面信號的影響造成運算出錯。因此目前支持DDR主板都是通過采用終結電阻來解決這個問題。由于每根數據線至少需要一個終結電阻,這意味著每塊DDR主板需要大量的終結電阻,這也無形中增加了主板的生產成本,而且由于不同的內存模組對終結電阻的要求不可能完全一樣,也造成了所謂的“內存兼容性問題”。 而在DDR-II中加入了ODT功能,當在DRAM模組工作時把終結電阻器關掉,而對于不工作的DRAM模組則進行終結操作,起到減少信號反射的作用,如下圖六所示。

圖六 ODT端接示意圖

ODT的功能與禁止由主控芯片控制,在開機進行EMRS時進行設置,ODT所終結的信號包括DQS、DQS#、DQ、DM等。這樣可以產生更干凈的信號品質,從而產生更高的內存時鐘頻率速度。而將終結電阻設計在內存芯片之上還可以簡化主板的設計,降低了主板的成本,而且終結電阻器可以和內存顆粒的“特性”相符,從而減少內存與主板的兼容問題的出現。

重置(Reset)

重置是DDR3新增的一項重要功能,并為此專門準備了一個引腳。這一引腳將使DDR3的初始化處理變得簡單。當Reset命令有效時,DDR3 內存將停止所有的操作,并切換至最少量活動的狀態,以節約電力。在Reset期間,DDR3內存將關閉內在的大部分功能,所有數據接收與發送器都將關閉,且所有內部的程序裝置將復位,DLL(延遲鎖相環路)與時鐘電路將停止工作,甚至不理睬數據總線上的任何動靜。這樣一來,該功能將使DDR3達到最節省電力的目的,新增的引腳如下圖七所示。

圖七 Reset及ZQ引腳

ZQ校準

如上圖七所示,ZQ也是一個新增的引腳,在這個引腳上接有一個240歐姆的低公差參考電阻。這個引腳通過一個命令集,通過片上校準引擎(ODCE,On-Die Calibration Engine)來自動校驗數據輸出驅動器導通電阻與ODT的終結電阻值。當系統發出這一指令之后,將用相應的時鐘周期(在加電與初始化之后用512個時鐘周期,在退出自刷新操作后用256時鐘周期、在其他情況下用64個時鐘周期)對導通電阻和ODT電阻進行重新校準。

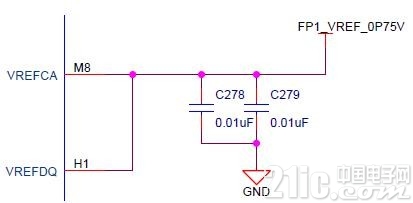

VREFCA VREFDQ

對于內存系統工作非常重要的參考電壓信號VREF,在DDR3系統中將VREF分為兩個信號。一個是為命令與地址信號服務的VREFCA,另一個是為數據總線服務的VREFDQ,它將有效的提高系統數據總線的信噪等級,如下圖八所示。

圖八 VREFCA VREFDQ

現在來說說DDR3和DDR4最關鍵的一些技術,write leveling以及DBI功能。

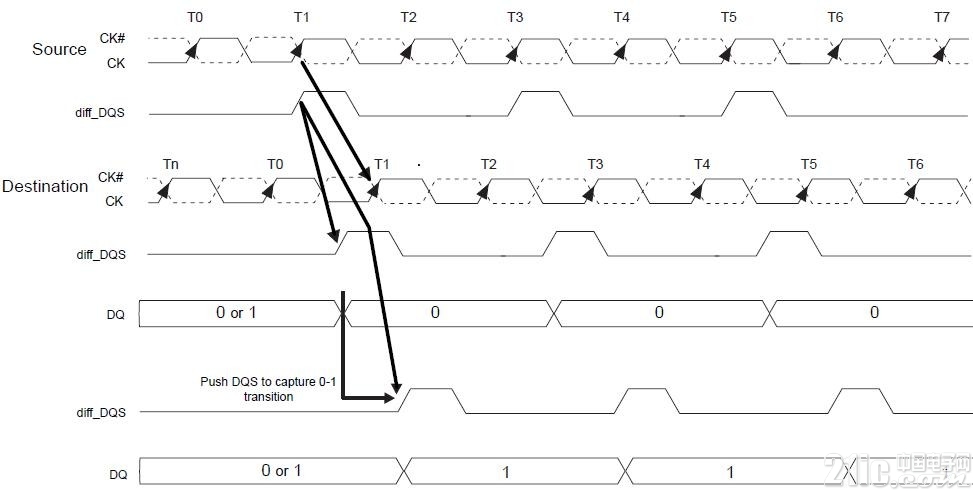

Write leveling功能與Fly_by拓撲

Write leveling功能和Fly_by拓撲密不可分。Fly_by拓撲主要應用于時鐘、地址、命令和控制信號,該拓撲可以有效的減少stub的數量和他們的長度,但是卻會導致時鐘和Strobe信號在每個芯片上的飛行時間偏移,這使得控制器(FPGA或者CPU)很難保持tDQSS、tDSS 和tDSH這些參數滿足時序規格。因此write leveling應運而生,這也是為什么在DDR3里面使用fly_by結構后數據組可以不用和時鐘信號去繞等長的原因,數據信號組與組之間也不用去繞等長,而在DDR2里面數據組還是需要和時鐘有較寬松的等長要求的。DDR3控制器調用Write leveling功能時,需要DDR3 SDRAM顆粒的反饋來調整DQS與CK之間的相位關系,具體方式如下圖九所示。

圖九、 Write leveling

Write leveling 是一個完全自動的過程。控制器(CPU或FPGA)不停的發送不同時延的DQS 信號,DDR3 SDRAM 顆粒在DQS-DQS#的上升沿采樣CK 的狀態,并通過DQ 線反饋給DDR3 控制器。控制器端反復的調整DQS-DQS#的延時,直到控制器端檢測到DQ 線上0 到1 的跳變(說明tDQSS參數得到了滿足),控制器就鎖住此時的延時值,此時便完成了一個Write leveling過程;同時在Leveling 過程中,DQS-DQS#從控制器端輸出,所以在DDR3 SDRAM 側必須進行端接;同理,DQ 線由DDR3 SDRAM顆粒側輸出,在控制器端必須進行端接;

需要注意的是,并不是所有的DDR3控制器都支持write leveling功能,所以也意味著不能使用Fly_by拓撲結構,通常這樣的主控芯片會有類似以下的描述:

DBI功能與POD電平

DBI的全稱是Data Bus Inversion數據總線反轉/倒置,它與POD電平密不可分,它們也是DDR4區別于DDR3的主要技術突破。

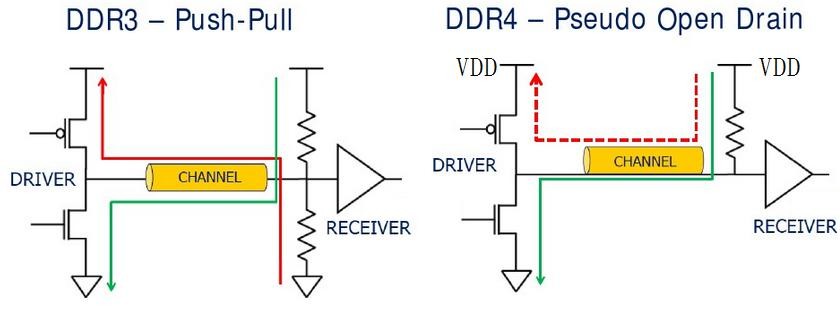

POD電平的全稱是Pseudo Open-Drain 偽漏極開路,其與DDR3對比簡單的示例電路如下圖十所示。

圖十 POD示意電路

從中可以看到,當驅動端的上拉電路導通,電路處于高電平時(也即傳輸的是“1”),此時兩端電勢差均等,相當于回路上沒有電流流過,但數據“1”還是照樣被傳輸,這樣的設計減少了功率消耗。

評論