如何基于設計Verilog FPGA 流水燈?

1 功能概述

本文引用地址:http://www.czjhyjcfj.com/article/201807/384018.htm流水廣告燈主要應用于LED燈光控制。通過程序控制LED的亮和滅, 多個LED燈組成一個陣列,依次逐個點亮的時候像流水一樣,所以叫流水燈。由于其形成美觀大方的視覺效果,因此廣泛應用于店鋪招牌、廣告、大型建筑夜間裝飾、景觀裝飾等。

在FPGA電路設計中,盡管流水燈的設計屬于比較簡單的入門級應用,但是其運用到的方法,是FPGA設計中最核心和最常用部分之一,是FPGA設計必須牢固掌握的基礎知識。從這一步開始,形成良好的設計習慣,寫出整潔簡潔的代碼,對于FPGA設計師來說至關(guān)重要。

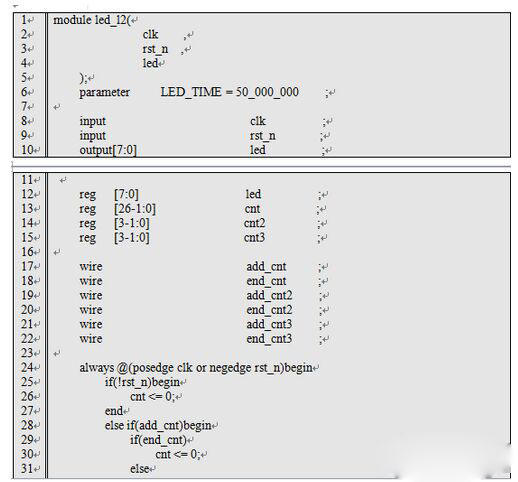

在本案例中,使用常用的verilog語言完成該程序,設計并控制8個燈的花式或循環(huán)點亮。具體功能要求如下:

上電后,實現(xiàn)左移和右移交替的流水燈。

右移流水燈:八個燈最左邊第一個燈滅,其他燈亮;隔1s后,第二個燈滅,其他燈亮;隔1s后,第三個燈滅,其他燈亮;如此類推,直到第八個燈滅1s后進行左移流水燈操作。

左移流水燈:八個燈最右邊第一個燈滅,其他燈亮;隔1s后第二個燈滅,其他燈亮;再隔1s后,第三個燈滅,其他燈亮;如此類推,直到第八個燈滅1s后進行右移流水燈操作。

2 設計思路

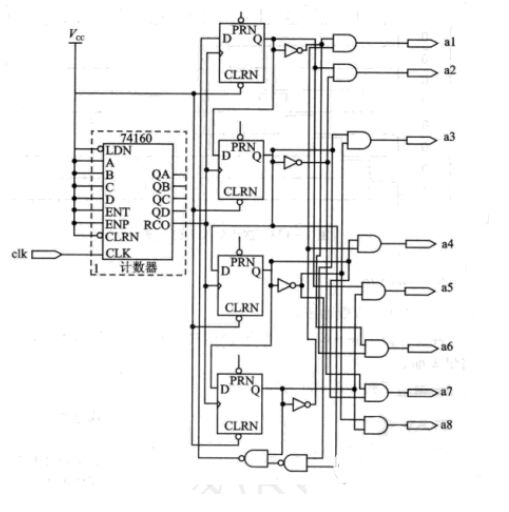

按照項目的功能要求,我們用8比特的LED信號表示8個燈,led[0]~led[7]分別代表第1個至第8個燈,值為0時亮,0時亮。下面我們來看看硬件電路圖以及制定出項目所需的信號列表。

圖1 流水燈硬件電路

信號列表:

評論