基于FPGA的高速光纖通信基帶板的設計

作者 袁行猛 徐蘭天 中國電子科技集團公司第四十一研究所(安徽 蚌埠 233010)

本文引用地址:http://www.czjhyjcfj.com/article/201806/382305.htm*基金項目:中國電科技術創新基金項目《微波毫米波大帶寬大規模MIMO測試技術研究》

袁行猛(1988-),男,助理工程師,研究方向:信號與信息處理。

摘要:基于FPGA ( Field Programmable Gate Array)的高速光纖傳輸系統設計出高速光纖通信基帶板。該基帶板使用Xilinx公司的Virtex-6系列芯片,使用FPGA中自帶的Aurora光口協議的IP核進行例化和設計,并選用了具有高速數據傳輸通信性能的光模塊進行數據傳輸,實際測試驗證了本設計工作可靠性,其功能完善能與更高的控制系統形成靈活對接。該基于FPGA的高速光纖通信基帶板是以創新基金項目為依托進行的設計,具體的設計成果能為從事采用FPGA開發光口的高速數據傳輸方面的工程人員提供較好的實用指導價值。

0 引言

隨著現代通信的發展,未來通信無論是有線通還是無線通信對數據的處理能力和數據的傳輸通信速率的要求都會越來越高,從現在的5G通信的要求中就能明確看到這個要求,所以尋求一種高速、穩定、可靠的通信方式成為現在的主要技術。光纖通信具有傳輸速度快、損耗低、容量大、占用帶寬低、抗電磁干擾的優點,非常適用于高速數據傳輸[1]。隨著現在Xilinx的FPGA芯片的快速發展,處理能力與功能日益增強,本設計選用Xilinx公司的Virtex6系列芯片,設計出具有4通道光口收發,每個通道速率高達6.25 Gb/s的基帶板卡,最終此基帶板總速率能達到4*6.25 Gb/s。本設計利用這兩個部分優勢,依附于實際的項目背景設計開發出高速光纖數據傳輸基帶板。最終驗證測試本設計的可靠與實用性,滿足項目的需求。

1 硬件架構設計

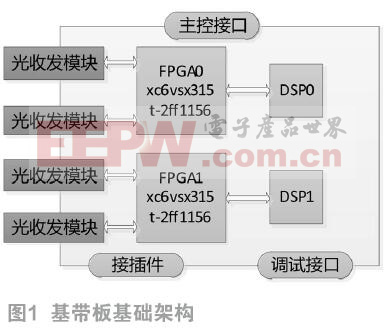

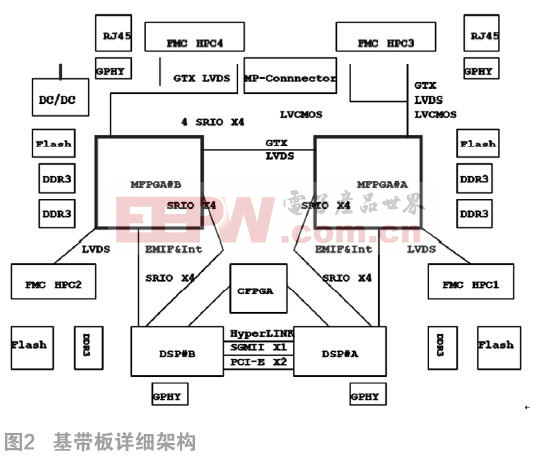

根據本次項目設計需求,本設計的目標是設計出基于FPGA的傳輸速率高達6.25 Gb/s的光纖數據通信板卡,該板卡上集成高性能FPGA和DSP,板卡能通過預留主控接口實現與上位機之間的通信,并通過DSP進行數據的收發,FPGA與DSP之間的速率通過FIFO進行匹配,最終由FPGA控制光口的通信以及數據的整理功能。由于本設計的速率和處理能力要求高,經過分析仿真,采用2個FPGA和2個DSP的組合處理架構,因此板卡硬件設計采用PCB+FPG(2)+DSP(2)+光模塊(4)的架構,并且預留出相應的接插件、主控、調試等接口,設計的基礎架構如圖1所示,詳細設計的架構如圖2所示。

在板卡設計中選取的FPGA是Xilinx公司的XC6VSX315T-2FF1156型號作為主控芯片用來控制光纖接口的主要功能,主要完成光收發模塊的使能控制、光傳輸的鏈路管理以及數據的傳輸。XC6VSX315T包含49200個Slices和25344 Block RAM,18個用戶I/O,可以滿足FPGA外圍電路設計和后期擴展與增強功能的設計[2]。設計中要求的光口傳輸速率是6.25 Gb/s,XC6VSX315T共有5組20個GTX數據收發接口,GTX通道的傳輸速率最快可達6.6 Gb/s,滿足技術指標中的信號傳輸速率的要求[3]。光收發模塊選用標準的成熟光收發模塊,該模塊最高傳輸速度可達4*6.25 Gb/s。整個板卡選用特定芯片完成主控與基帶板之間的數據交互,從而來控制板卡的主要功能。

2 軟件架構設計

本次設計基于FPGA的高速光纖通信基帶板卡時就采用了Verilog硬件描述語言來作為設計語言,Verilog語言因其容易操作、簡單易讀、穩定可靠等優越點,在電子自動化設計(EDA)技術的迅猛發展中成為主流語言,也是目前使用最為廣泛的硬件描述語言。因此,在本設計中,采用標準的FPGA邏輯設計的基本方式,模塊化相應的功能,根據功能進行模塊劃分,設計中總體分成一個頂層模塊和三個子模塊。頂層模塊主要調用各子模塊和設計數據接口,三個子模塊為全局時鐘管理模塊、數據控制與整理模塊和Aurora 8B10B IP核的調用模塊。本次光口數據傳輸過程中使用的協議是Xilinx公司提供的一種免費的數據鏈路層協議——Aurora協議,該協議已經驗證是穩定可靠的傳輸協議,已得到實際應用,該協議核內部封裝了高速串行數據接口硬核,可編程邏輯器件通過綁定GTX通道進行數據的收發交互。單個GTX通道的數據傳輸速率可達G bit級別,根據不同的需求可以實現多個通道的組合使用,從而可實現幾十G bit,甚至上百G bit速率的數據傳輸。因此,本次設計中FPGA邏輯設計的核心模塊就采用了Aurora 8B10B IP核。

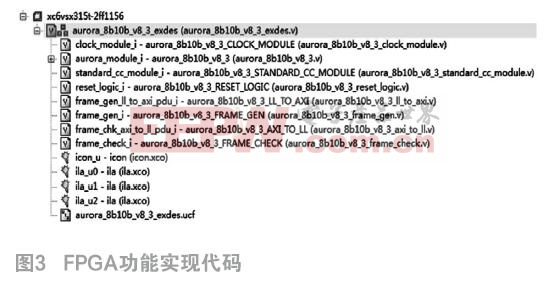

通過例化Aurora 8B10B IP核,生成特定功能需求的模塊,數據位寬256位,如圖3所示,是主要的FPGA的功能實現代碼模塊部分。

其中主要實現部分有:頂層模塊(aurora_8b10b_v8_3_exdes)、全局時鐘管理模塊(aurora_8b10b_v8_3_CLOCK_MODULE)、光口通信模塊(aurora_8b10b_v8_3)、測試數據控制與產生模塊(aurora_8b10b_v8_3_FRAME_GEN)、工程約束文件(aurora_8b10b_v8_3_exdes.ucf)等。

3 光口的IP核協議

3.1 Aurora協議

Aurora協議是由Xilinx公司開發的光纖傳輸中的串行傳輸數據的一個鏈路層協議。它具有高帶寬、可擴展性等突出特點已得到實際廣泛應用[4]。此外,該協議的幀數據結構也相對簡單,數據組包效率較高。因此,它非常適用于點對點的數據傳輸環境。通常的光口通信鏈路channel中都會有若干個子lane通道組成,其中每個lane又能實現數據的雙工傳輸。所以本設計中的Aurora協議接口就在Xilinx公司的Virtex-6芯片上實現。

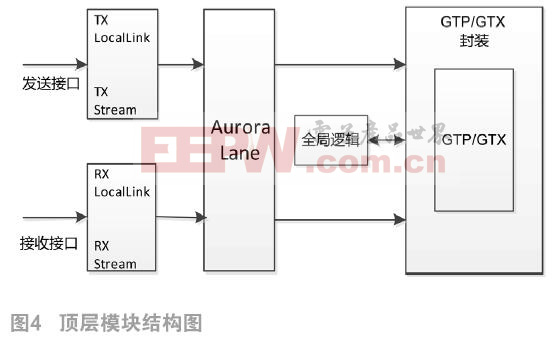

Aurora 8B/10B頂層模塊例化了Aurora 8B/10B通道模塊、TX和RX本地鏈路模塊、全局邏輯模塊以及GTP/GTX收發器。在設計中通過例化IP核會自動生成這些對應模塊,具體的頂層模塊結構如圖4所示。

3.2 8B/10B編解碼

8B/10B編碼是一種高性能的串行數據編碼方式,8B/10B編碼的基本特征就是保證編碼過程中的DC(直流)平衡,其基本的編碼功能就是將8 bit輸入數據經過映射編碼成10 bit的數據輸出,這種編碼方式能使數據中“1”和“0”的總個數平衡下來,使其總數最大不超過2,且連續的“1”或“0”的個數不超過5位這樣就保證了傳輸過程中信號的變換頻率能保持在一個足夠高的水平上。編碼的方式是將數據位中的連續8位數據分解成5位和3位的高低兩組數據,然后將數據中的低5位信號和高3位的信號分別通過5B/6B編碼和3B/4B編碼變換成6位和4位信號,然后在合并成一個10 bit的信號輸出,以上就是8B/10B編碼的基本編碼思路。正是因為其具有能讓命令信息流頻譜分量為0或近乎為0和確保時鐘恢復等優點,所以光纖數據傳輸中采用了8B/10B編碼。

編碼的作用是提高數據傳輸的可靠性,因為8B/10B編碼的以上優點以及此編碼的特性,在光纖通信系統中大都采用8B/10B編碼作為主要數據編碼方式進行數據傳輸,從而來保證光纖通信中的數據可靠性,隨著技術的發展與實際的應用進展,到目前為止,8B/10B編碼也日漸成熟可靠,優點也被充分的利用,也是光口協議中的標準編碼形式,本次數據傳輸中仍采用成熟的8B/10B編碼,數據的可靠性能得到充分保障[5]。

4 基帶板功能的驗證

基帶板設計完成后進入基帶板測試驗證階段,相應的電路連線完成后,在光口插入相應的光模塊,用光纖連接完成后,加載程序,然后用Xilinx自帶的觀測軟件Chipscope觀測光口的實際發送與接收到的數據。

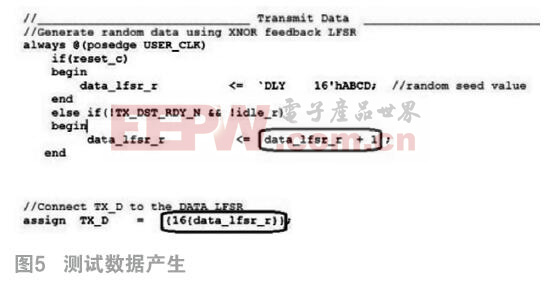

數據端控制為了驗證設計的傳輸的可靠性,手動編寫了測試文件,用來傳輸數據,如圖5所示做一個16位累加數(data_lfsr_r),然后數據整理成16*16的256位數據(TX_D),經過光口的發送后,在接收端觀測驗證。

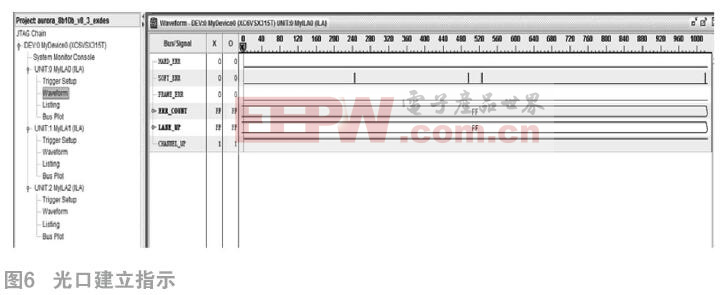

在Chipscope端觀測光口鏈路的建立情況以及數據的收發情況,如圖6所示,光口通路的建立情況,圖中CHANNEL_UP顯示為1,說明鏈路建立成功,光口正常工作。

隨后對光口的發送與接收到數據進行觀測,使整個基帶板運行起來后,實時觀測數據的傳輸情況,如下圖7所示,發送的是256位16進制數(tx_d_i),由于數據位寬較大觀測不方便,根據我們的設計思路,設計中的實際位寬是256位,測試中發送的256位數據是由低16位數組合而成,為了觀測方便取出低16位數據(tx_d_i[0:15])觀測,為了方便比對輸入輸出數據,編寫測試數據,這里設計的是連續發送的由16位累加數數組合而成的256位數據,通過觀測比對光口接收數據(rx_d_i)發現,接收到的也是標準累加數,從而驗證光口建立成功,數據收發正常,也驗證了基帶板設計的功能完整性,證實了此次設計的合理與實用性。

設計的基帶板中包含兩個高性能的Virtex-6 FPGA和兩個DSP,FPGA+DSP的聯合可以進行數據的高速處理,整套基帶板具有完善的數據處理與傳輸能力,這樣就設計出了一整套功能完善的基帶板卡。

5 結論

本文設計了一種基于FPGA的高速光纖通信基帶板,主要基于光口的高速通信,使用Verilog硬件描述語言設計的一種滿足項目需求的基帶板,該板卡具有高性能的數據處理能力和高速的傳輸通信能力,通過實際上板測試,驗證了板卡設計的合理性與正確性,滿足了實際項目需求,該基帶板的設計可以為通信中的高速傳輸板卡的設計工作者們提供較高的指導意義。

參考文獻:

[1]趙梓森.光纖通信的過去、現在和未來[J].光學學報,2011,31(9):99-101.

[2]Xilinx.Virtex-6 Family Overview [Z].America: Xilinx Inc,2015.

[3]Xilinx,Virtex-6 FPGA GTX Transceiver Wizard [Z].America:Xilinx Inc,2018.

[4]候春雷,唐碧華,胡鶴飛,等.基于Aurora的MAC層幀結構的設計與實現[J],中國科技論文在線.2010 (1).

[5]章潔.基于FPGA的高速光纖通信IP核研究設計[J].數字技術與應用,2015,5:29-30.

本文來源于《電子產品世界》2018年第7期第58頁,歡迎您寫論文時引用,并注明出處。

評論