14張圖看懂半導體工藝演進對DRAM、邏輯器件、NAND的影響

編者按:DRAM工藝尺寸的縮減正在面臨基本的物理限制,目前還有沒有明確的解決方案,由于印刷需求的推動,DRAM的清洗復雜度也在增加。

邏輯器件

本文引用地址:http://www.czjhyjcfj.com/article/201804/378381.htm在第八張幻燈片中,我介紹了格羅方德、英特爾、三星和臺積電的邏輯器件工藝節點。這四家廠商是邏輯器件工藝領域的領導廠商。應當特別指出的是,英特爾的節點通常等同于其他廠商下一代較小的工藝節點,比如英特爾的10nm和代工廠的7nm差不多。

幻燈片表格下方,左側顯示的是FinFET的橫截面,這是當前先進邏輯器件首選的工藝,右側顯示了納米線和納米片,預計將在4nm左右時替代FinFET。

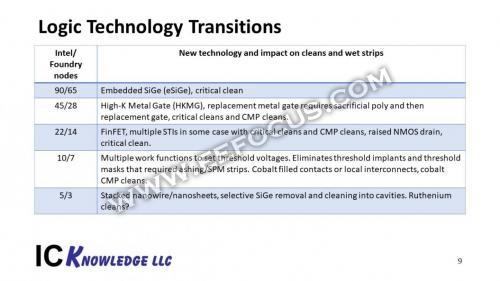

在幻燈片9中,我介紹了一些主要的邏輯器件工藝的演變。在這張幻燈片中,我以英特爾/代工廠的兩個數字展示工藝節點,如上所述,英特爾的工藝節點和代工廠較小尺寸的工藝節點類似。

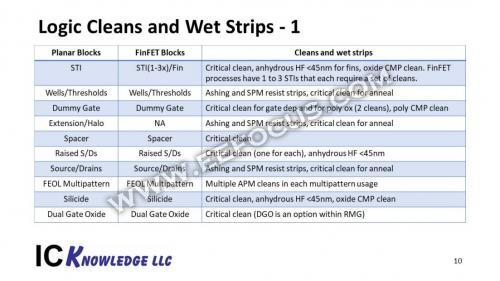

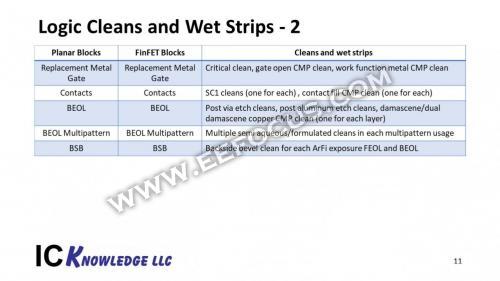

在第10張和第11張幻燈片中,我介紹了一些主要的邏輯工藝模塊,并討論了這些模塊對清洗和濕條帶的需求。

12號幻燈片是邏輯器件章節最后一張幻燈片,介紹了基于臺積電工藝節點的清洗步驟數量。當工藝尺寸下降到第一代7nm工藝時,由于增加了掩膜層,再加上多重圖案化的復雜性,清洗次數一直在增加,在隨后的7nm+和5nm節點上,由于EUV將顯著降低光刻的復雜度,因此消除了許多清洗步驟。

評論