手把手教你FPGA與RT以及Host端通信

在ECM中,會涉及到FPGA、RT以及主機,那么三者之間是如何進行數據流的傳輸呢?本文將以cRIO-9068為例,帶大家了解整個編程以及實現過程。

本文引用地址:http://www.czjhyjcfj.com/article/201710/365494.htm一、FPGA、RT以及主機數據流之間的通信概覽

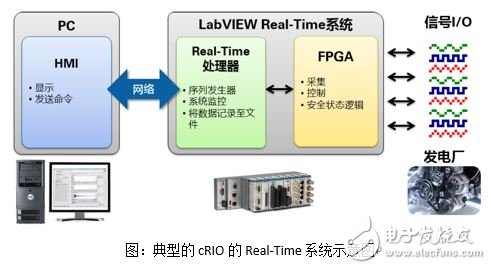

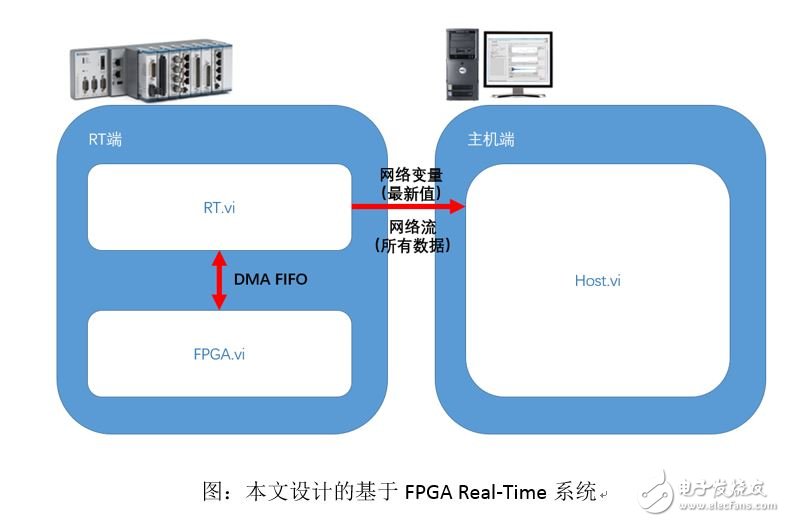

在一個含FPGA的Real-TIme系統中,FPGA負責采集信號,然后將采集的數據傳輸至RT端進行監控、處理,同時在主機進行數據的顯示、記錄或者發送命令。典型的基于cRIO的Real-TIme系統如下圖所示:

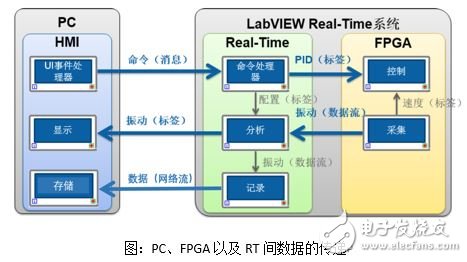

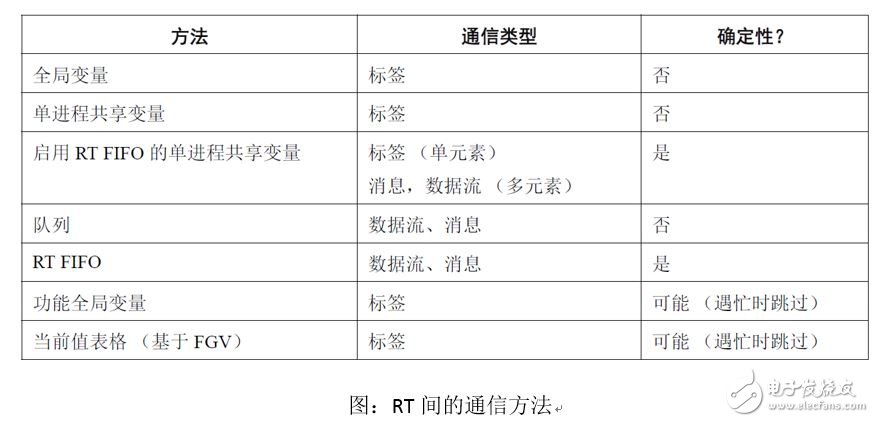

數據在Real-TIme系統中主要分為兩種,一種是比如消息,命令等等,此類數據我們只關注其最新的值,主要通過標簽、消息進行數據的傳遞;另外一種是數據流,我們需要獲取所有的數據信息,而不僅僅是最新值,主要通過網絡流、FIFO進行傳遞。

對于采集卡采集到的數據,我們有時候是希望對其進行記錄,并在Host端進行顯示觀測。通常,FPGA與RT是通過FIFO進行數據流的傳輸,而RT則采用網絡流與主機傳輸數據。本文將以cRIO-9068為例,展示從信號采集到上位機顯示的整個過程,幫助大家更好地了解Real-TIme系統的數據處理方式

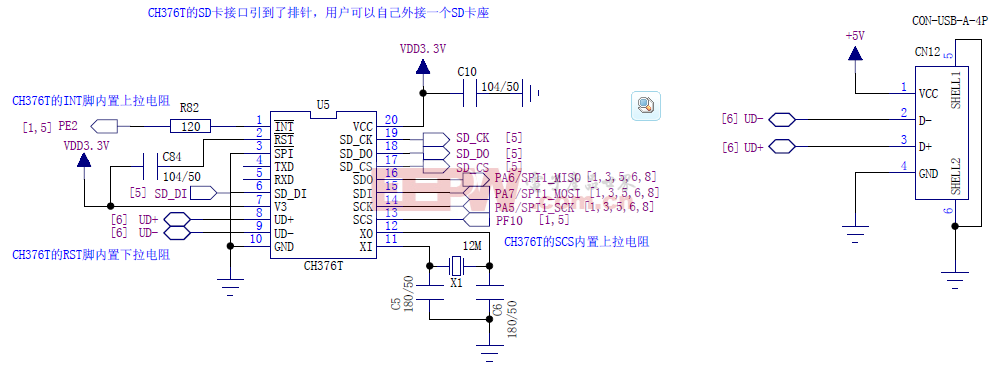

二、硬件軟件

數采卡:NI 9263

設備:cRIO-9068;RIGOL示波器

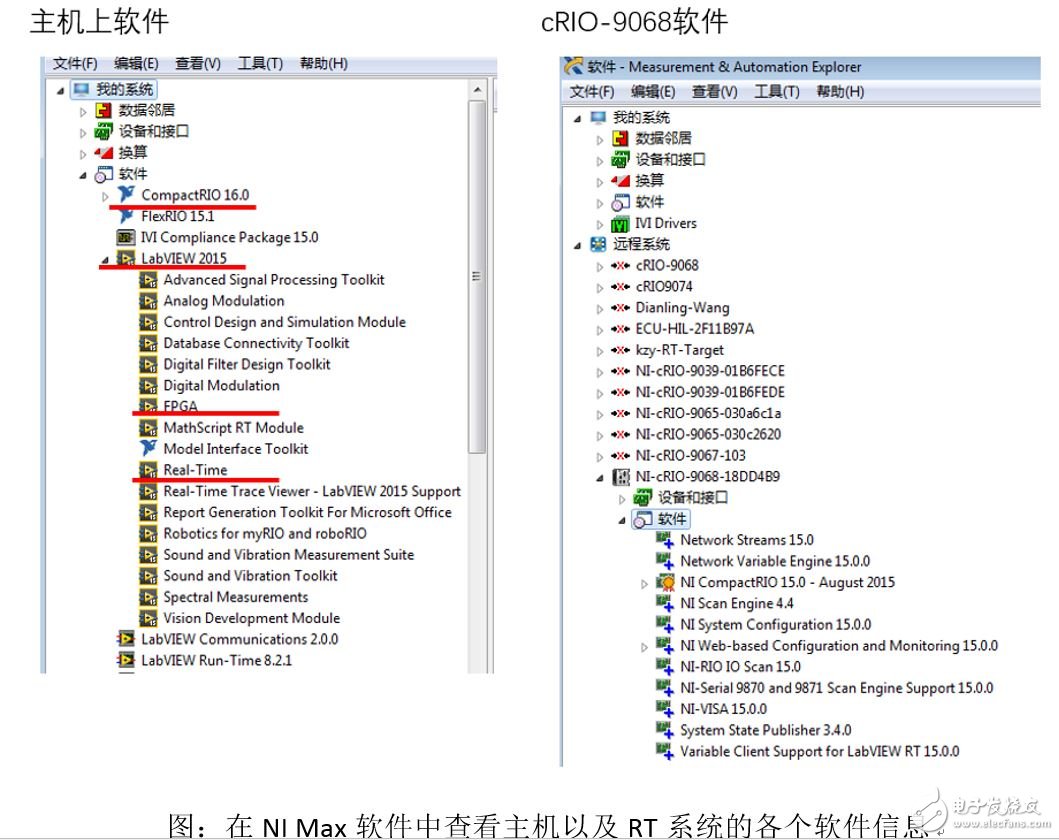

軟件:LabVIEW; LabVIEW Real-Time;LabVIEW FPGA;CompactRIO

(可以在NI Max中查看自己所安裝的軟件、驅動以及模塊的版本,保持cRIO-9068中的軟件版本正確)

最終,硬件連接如圖。

三、設計過程

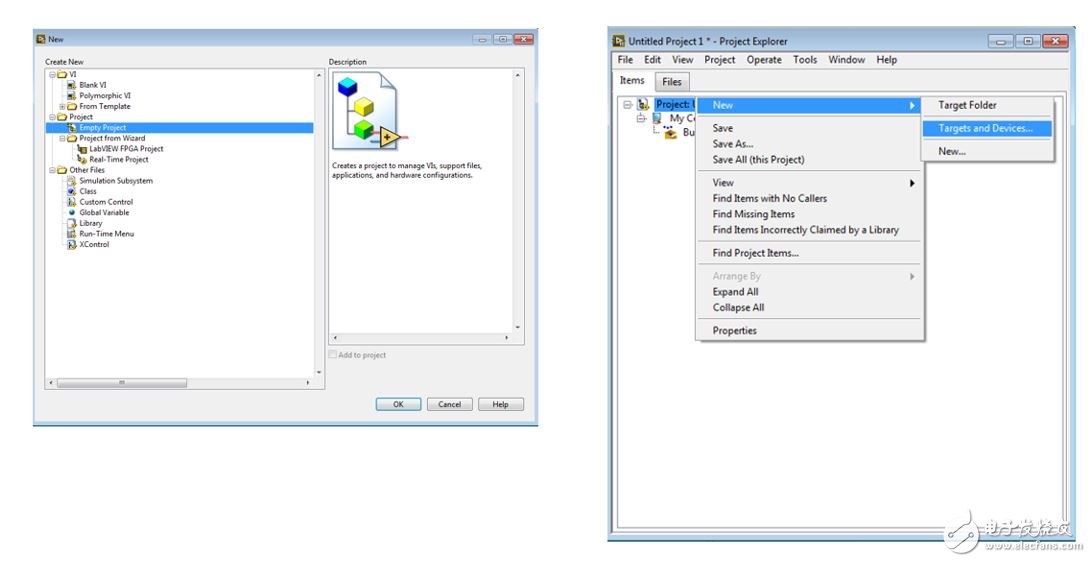

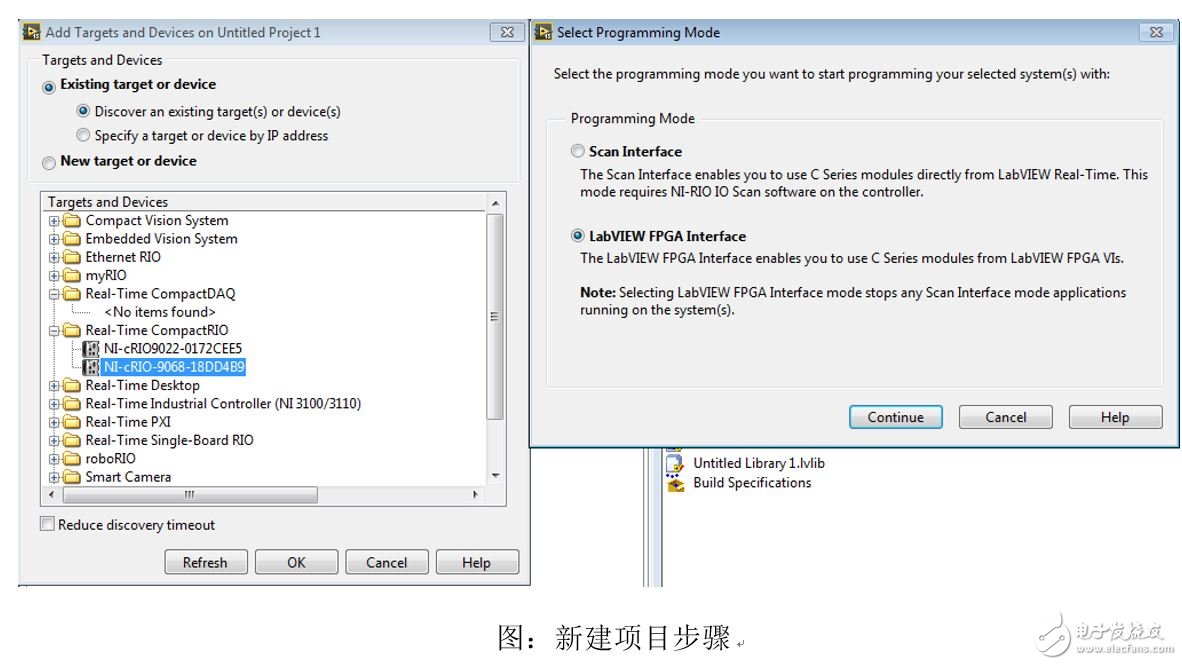

1)新建項目

打開LabVIEW,新建項目,在項目瀏覽器中,右鍵我的項目,選擇添加目標設備,將硬件cRIO-9068以及NI 9263一并添加入新建的項目。

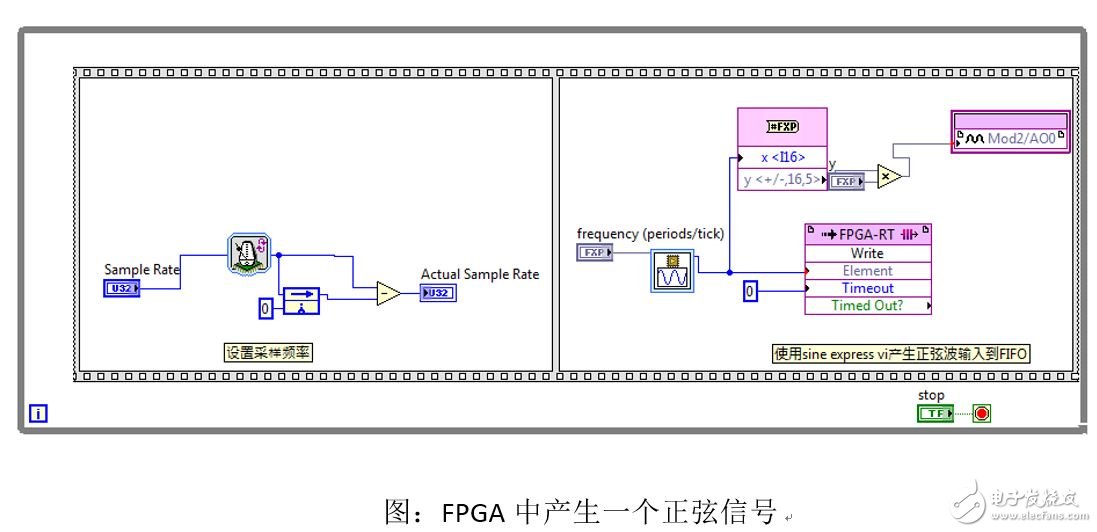

2)FPGA.vi的設計

首先我們需要在FPGA中產生一個正弦信號,經由NI 9263的模擬端口輸出。

注意:此處不能使用單周期定時循環,因為該vi無法在一個時鐘滴答內完成執行。關于單周期定時循環參考鏈接:

由于要將FPGA產生的正弦波信號傳到RT端進行顯示等處理,屬于數據流的傳輸,因此我們在此處使用DMA FIFO()。

在項目瀏覽器中FPGA下右鍵新建一個FIFO,其FIFO設置如下:

其中在Type處選擇類型:Target to Host-DMA,大小使用默認的即可。在Data Type中選擇數據的類型,此處我們傳輸的是無符號的32位數據,因此選擇U32即可。

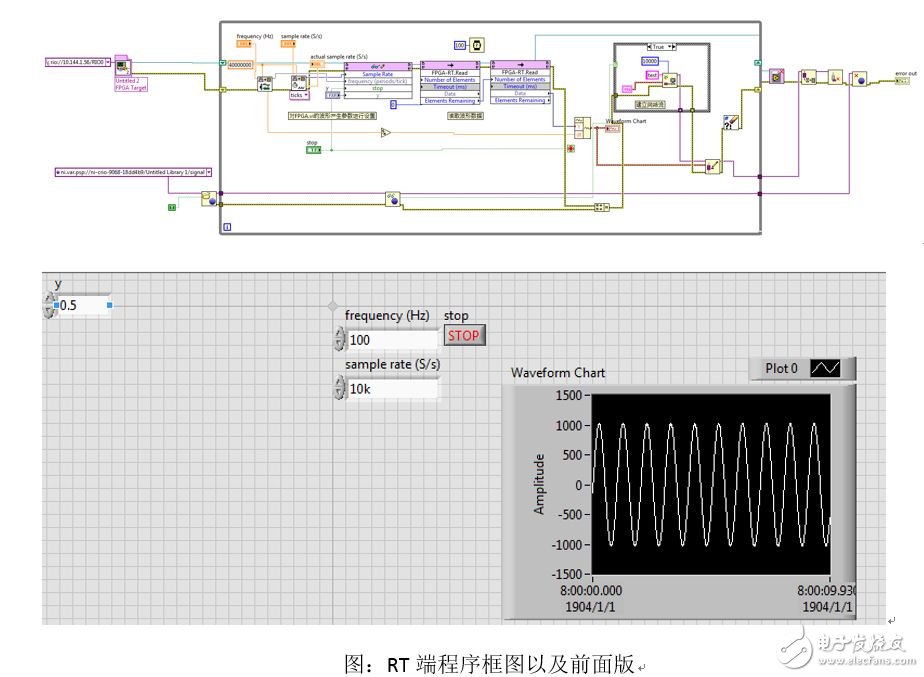

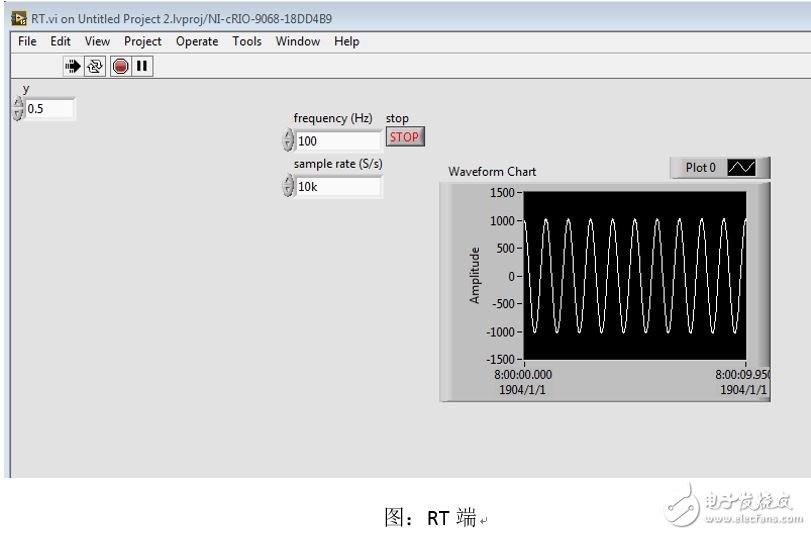

3)RT.vi的設計

RT端的vi主要由兩部分組成,一部分是從FIFO中讀取從FPGA傳來的數據,一部分是建立網絡流,將數據傳給主機進行檢測。這里要注意的是,由于我們需要的是打開主機隨時讀取數據,主機程序運行時候。

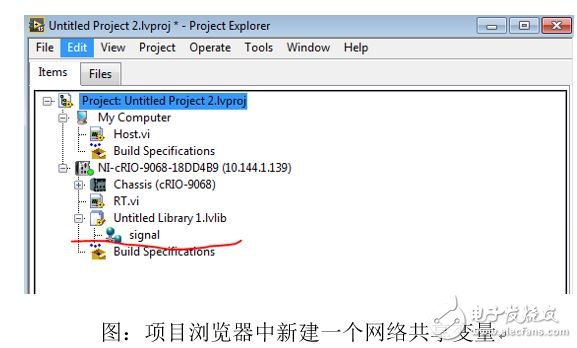

RT端的vi主要由兩部分組成,一部分是從FIFO中讀取從FPGA傳來的數據,一部分是建立網絡流,將數據傳給主機進行檢測。這里要注意的是,由于我們需要的是打開主機隨時讀取數據,主機程序運行時候,會產生一個信號,使RT端的網絡流端建立并且寫入數據。因此,我們新建一個布爾變量,作為這個傳遞信號。

因此,在RT端,我們對主機的數據傳遞主要使用了兩種方式,一種是網絡流,用于每一個數據傳遞;另一個是網絡變量,獲取布爾控件的最新值。

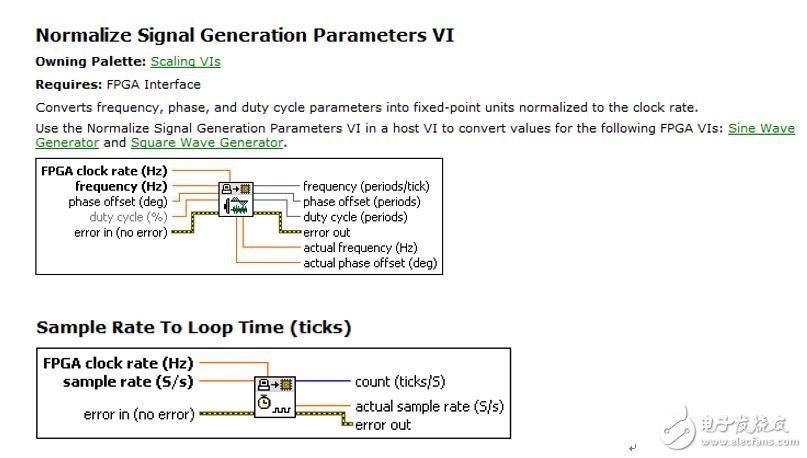

在FIFO波形的傳遞過程中,經常使用到以下兩個數,這里做多一些的介紹。

Normalize Signal Generation Parameters Sample Rate To Loop Time

這兩個會經常搭配使用,主要是對FPGA部分產生波形的波形參數進行設置,其中主要是對波形的頻率以及采樣頻率(在FPGA端則需要使用Loop Time函數),后面會連接使用“Write/Read Control”節點。

在網絡流的設置中,按照常規:建立寫端-寫入-關閉的順序,其中注意的是,主機在建立的時候設置超時(Time out)默認是-1,會無限時間的等待下去。且寫入端的名字不能和讀取端的名字有重合部分,不然會報錯的。

至此,我們完成了RT端以及FPGA的程序編寫。但是,在有些情況下,我們會希望cRIO里面的程序固定,上電即可運行(比如上電即可采集或者產生波形),而我們可以隨意的不定時的使用主機通過局域網隨機抓取一段cRIO數據,因此我們需要在主機上(host端)新建一個vi實現此功能。

為了方便起見,此處新建的主機vi和RT等程序放在一個項目內,實際應用中新建一個項目,在新的項目中編寫主機的代碼。

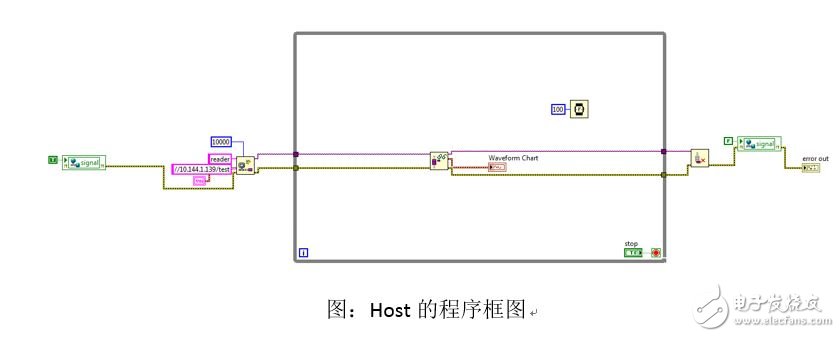

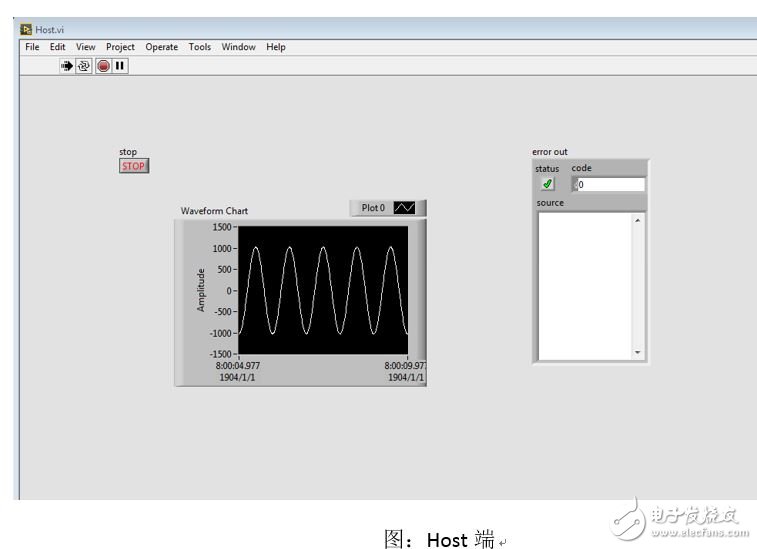

4)Host.vi的設計

在主機上,我們這里簡單的只是讀取,首先會賦值給共享變量在從而在RT端建立網絡流寫入端寫入數據。

5)整個系統顯示如下

評論