嵌入式系統VGA顯示接口的系統實現,軟硬件解決方案

- 設計摘要

在許多嵌入式系統中,為了實現良好的人機界面,這就對系統的MCU和顯示設備提出了更高的要求。若能用低速的MCU實現和PC機類似的顯示效果,將會大幅度提高產品的附加值。目前,帶有VGA接口和類VGA的顯示設備隨處可見,若能以此類設備作為各種嵌入式系統的顯示器,也可提高各種嵌入式設備人機界面的通用性。本項目采用FPGA器件和帶有VGA接口的顯示器,實現適用于各種嵌入式系統的顯示接口,使得低速的MCU不需要增加過多開銷即可采用VGA接口設備作為顯示器。

- 硬件結構圖

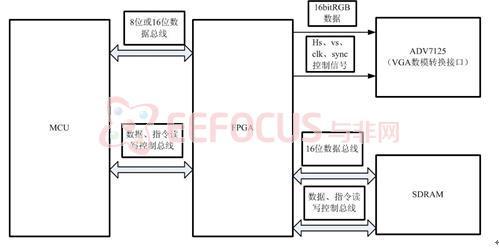

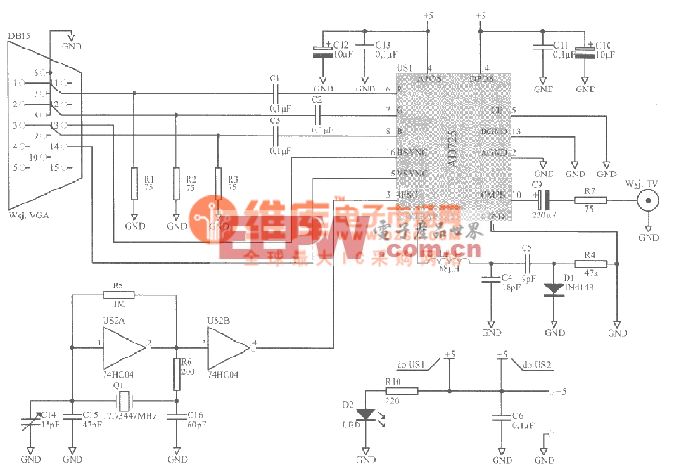

系統硬件結構圖如圖1所示:

圖1系統硬件結構圖

三、軟件介紹

系統軟件分為兩個部分:MCU軟件模塊和FPGA軟件模塊。MCU軟件模塊主要負責將要顯示數據傳送給FPGA,主要實現的功能是在VGA顯示器上打點(在指定的行坐標、列坐標出以某一指定的顏色顯示一個點),在此功能的基礎之上實現劃線、矩形填充、顯示圖片的功能。FPGA模塊主要負責接收MCU模塊發送的數據,并將接收到的數據通過內部的寫FIFO單元存入外接的SDRAM存儲器中,然后再通過內部的讀FIFO單元從SDRAM中將數據取出送到VGA數模轉換模塊,同時FPGA模塊還要提供VGA顯示所需要的HS、VS、SYNC等掃描信號。

1、FPGA軟件模塊介紹

FPGA模塊的軟件主要有以下幾部分組成。

- FPGA頂層模塊:

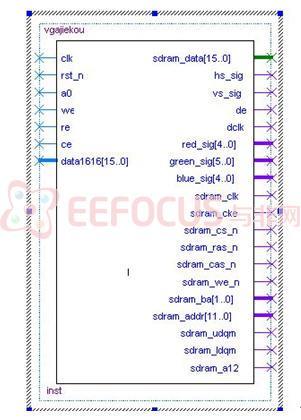

FPGA頂層模塊主要定義了FPGA與外圍的MCU、SDRAM、VGA數模轉換的接口。各引腳的具體定義如表1和圖1所示。

表1

方向 | 名稱 | 描述 |

Input | clk | 輸入時鐘50M |

Input | rst_n | 異步復位,低有效 |

Input | a0 | 數據地址選擇,低表示地址 |

Input | we | 寫信號,上升沿有效 |

Input | re | RE,讀信號,下降沿有效 |

Input | ce | 片選,低有效 |

input | [15:0]data1616 | 時序接口,數據線 |

output | dclk | 輸出時鐘40M,給VGA |

output | hs_sig | 列同步信號 |

output | vs_sig | 行同步信號 |

output | red_sig[4:0] | 紅信號 |

output | green_sig[5:0] | 綠信號 |

output | blue_sig[4:0] | 藍信號 |

output | sdram_clk | SDRAM時鐘信號 |

output | sdram_cke | SDRAM時鐘有效信號 |

output | sdram_cs_n | SDRAM片選信號 |

output | sdram_ras_n | SDRAM行地址選通脈沖 |

output | sdram_cas_n | SDRAM列地址選通脈沖 |

output | sdram_we_n | SDRAM寫允許位 |

output | sdram_ba[1:0] | SDRAM的L-Bank地址線 |

output | sdram_addr[12:0] | SDRAM地址總線 |

inout | sdram_data[15:0] | SDRAM數據總線 |

output | sdram_udqm | SDRAM高字節屏蔽 |

output | sdram_ldqm | SDRAM低字節屏蔽 |

圖1 FPGA軟件頂層模塊

- SDRAM讀、寫控制模塊

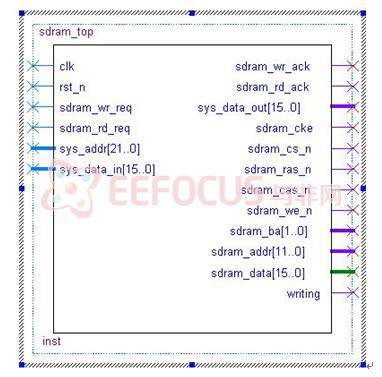

SDRAM讀、寫控制模塊主要實現FPGA對SDRAM存儲器的讀寫控制,該模塊主要完成SDRAM的上電初始化以及定時刷新、讀寫控制等狀態的變遷。該模塊各引腳的具體定義如表2和圖2所示。

表2

方向 | 名稱 | 描述 |

input | clk | 系統時鐘,100MHz |

input | rst_n | 復位信號,低電平有效 |

input | sdram_wr_req | 系統寫SDRAM請求信號 |

input | sdram_rd_req | 系統讀SDRAM請求信號 |

output | sdram_wr_ack | 系統寫SDRAM響應信號 |

output | sdram_rd_ack | 系統讀SDRAM響應信號 |

input | sys_addr[21:0] | 讀寫SDRAM時地址暫存器 |

input | sys_data_in[15:0] | 寫SDRAM時數據暫存器 |

output | sys_data_out[15:0] | 讀SDRAM時數據暫存器 |

output | writing | SDRAM正寫標志 |

output | sdram_clk | SDRAM時鐘信號 |

output | sdram_cke | SDRAM時鐘有效信號 |

output | sdram_cs_n | SDRAM片選信號 |

output | sdram_ras_n | SDRAM行地址選通脈沖 |

output | sdram_cas_n | SDRAM列地址選通脈沖 |

output | sdram_we_n | SDRAM寫允許位 |

output | sdram_ba[1:0] | SDRAM的L-Bank地址線 |

output | sdram_addr[11:0] | SDRAM地址總線 |

inout | sdram_data[15:0] | SDRAM數據總線 |

圖2 SDRAM頂層模塊

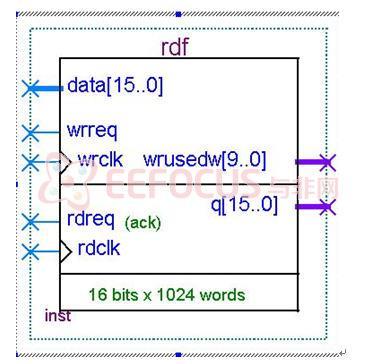

- 讀、寫FIFO模塊

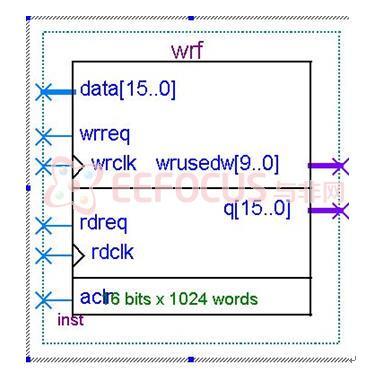

讀、寫FIFO模塊采用系統的IP核實現,FIFO的容量為1K字單元(16位)。Wrf FIFO單元在wrreq為1時將MCU的數據存入wrf

FIFO,數據存入后,立即被寫入SDRAM中。Rdf FIFO單元在rdreq為1時將數據從SDRAM中取出送給VGA控制模塊。

圖3 寫FIFO模塊

圖4 讀FIFO模塊

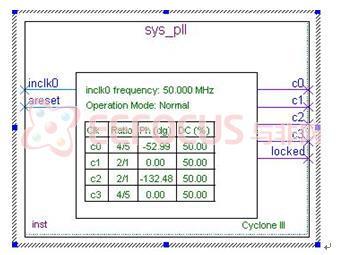

- PLL單元

PLL單元主要負責管理系統所需的各種時鐘信號,其中主要有:inclk0為系統輸入時鐘(50MHZ)。c1、c2為SDRAM提供100MHZ的讀、寫時鐘。c0、c3分別是為采樣MCU數據和VGA時序掃描所提供的40MHZ時鐘。

圖5 PLL模塊

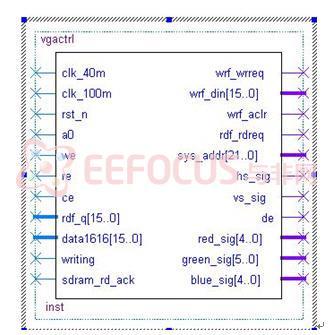

- VGA控制模塊

VGA控制模塊主要負責將從MCU接收到的數據送給wrf FIFO中,然后從rdf FIFO中取出要顯示的數據,并產生VGA所需的行掃描、列掃描信號、同步信號、時鐘信號,一并送給外圍的VGA數模轉換電路。該模塊的各引腳的具體定義如表3和圖6所示。

表3

方向 | 名稱 | 描述 |

input | clk_40m | 輸入時鐘40M |

input | clk_100m | 輸入時鐘100M |

input | rst_n | 異步復位,低有效 |

input | a0 | 數據地址選擇,低表示地址 |

input | we | 寫信號,上升沿有效 |

input | re | 讀信號,下降沿有效 |

input | ce | 片選,低有效 |

input | rdf_q[15:0] | rdf讀數據 |

input | writing | 正寫SDRAM |

input | sdram_rd_ack | 讀SDRAM應答 |

input | data1616[15:0] | 數據線 |

output | wrf_din[15:0] | wrf寫數據 |

output | wrf_wrreq | wrf寫使能 |

output | wrf_aclr | wrf異步清零 |

output | [21:0]sys_addr | SDRAM地址 |

output | rdf_rdreq | rdf讀使能 |

output | hs_sig | 列同步信號 |

output | vs_sig | 行同步信號 |

output | de | 時序控制 |

output | red_sig[4:0] | 紅信號 |

output | green_sig[5:0] | 綠信號 |

output | blue_sig[4:0] | 藍信號 |

圖6 VGA模塊

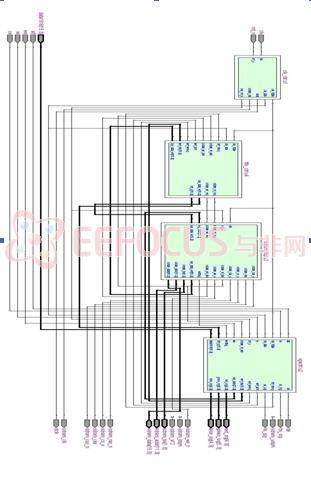

2、系統的RTL圖

評論