函數信號發生器和示波器二合一儀器設計,提供源碼

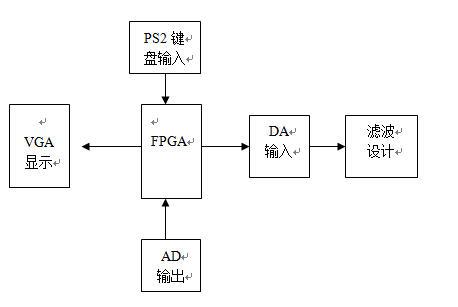

1.總體設計方案

1.1 主控制模塊

方案一:采用單片機。單片機的應用較為廣泛,但是單片機的處理頻率達不到我們的要求。所以我們只能夠使用處理速度較快的處理器。

方案二:采用Xilinx的FPGA來實現主控制器。Xilinx的FPGA的內部IP核可以方便的產生DDS波形,這樣就方便我們能夠更好的產生想要的波形。

所以采用方案二。

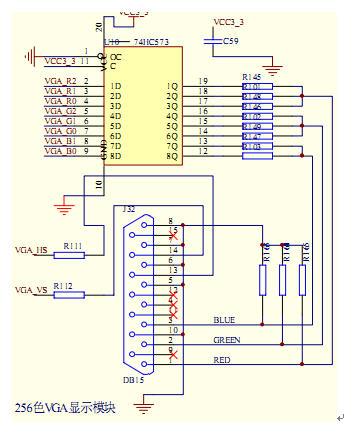

1.2顯示模塊

方案一:使用TFT觸摸屏。彩屏有這樣明顯的優點:微功耗,尺寸小,超薄輕巧,顯示信息量大,字跡美觀,視覺舒適,但是對于FPGA來說,其實現對觸摸屏的控制不能夠較好的完成控制要求。

方案二:使用VGA顯示。FPGA可以實現對VGA的控制。VGA的使用較為廣泛,且價格在接收的范圍之內。而且,對于FPGA來說,實現對VGA接口的控制比控制其他的顯示器更加的方便和快捷。這就節省了我們的設計麻煩。

所以采用方案二。

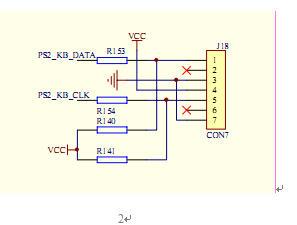

1.3 輸入模塊

方案一:使用矩陣鍵盤。矩陣鍵盤的編碼較為簡答,且可以實現較為復雜的控制。但是矩陣鍵盤的按鍵過少,不能夠實現更多數據的輸入。

方案二:使用PS2鍵盤。PS2鍵盤的控制更為簡單,我們可以通過兩根數據線精心數據的讀取,且PS2鍵盤的設計更加符合我們設計要求,這就決定了PS2在本設計中的優勢。

故采用方案二。

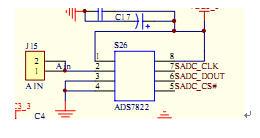

1.4 AD輸出模塊

ADS7822是一種單片高速12位逐次比較型A/D轉換器, ADS7822內置雙極性電路構成的混合集成轉換顯片,具有外接元件少,功耗低,精度高等特點,并且具有自動校零和自動極性轉換功能,只需外接少量的阻容件即可構成一個完整的A/D轉換器。所以該方案采用ADS7822作為AD輸入的元器件。

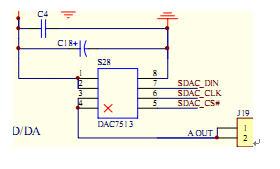

1.5 DA輸出模塊

DAC7513是8分辨率的D/A轉換集成芯片。與微處理器完全兼容。這個DA芯片以其價格低廉、接口簡單、轉換控制容易等優點,在單片機應用系統中得到廣泛的應用。D/A轉換器由8位輸入鎖存器、8位DAC寄存器、8位D/A轉換電路及轉換控制電路構成。

2.程序設計

2.1 AD輸出

--**********************分頻進程*************************

process(clk)

variable cnt1 : integer range 0 to 100;

variable cnt2 : integer range 0 to 20;

begin

if clkevent and clk=1 then

if cnt1=100 then

cnt1:=0;

if cnt2=20 then

cnt2:=0;

clock=not clock;

if(cnt=3)then

cnt=0;

else

cnt=cnt+1;

end if;

else

cnt2:=cnt2+1;

end if;

else

cnt1:=cnt1+1;

end if;

end if;

end process;

--**************狀態驅動進程**********************

sync :process(clock,reset)

begin

if(reset = 0) then

current_state = start;

elsif(clockevent and clock=1) then

current_state = next_state;

end if;

end process sync;

--***************adc驅動進程*******************

comb :process(current_state, intr)

begin

case current_state is

when start => --啟動狀態

next_state = convert;

cs = 0;

wr = 0;

rd = 1;

read_data = 0;

when convert =>--初始化

if(intr = 0) then

next_state = read1;

else

next_state = convert;

end if;

cs = 1;

wr = 1;

rd = 1;

read_data = 0;

when read1 =>--讀狀態1

next_state = read2;

cs = 0;

wr = 1;

rd = 0;

read_data = 1;

when read2 =>--讀狀態2

next_state = start;

cs = 1;

wr = 1;

rd = 1;

read_data = 0;

when others =>--其他狀態

next_state = start;

end case;

end process comb;

--****************讀取AD數據********************

get_data: process(clock,reset)

begin

if(reset = 0) then

p=0;

elsif(clockevent and clock=1) then

if(read_data = 1) then

p=conv_integer(data_i);

end if;

end if;

end process;

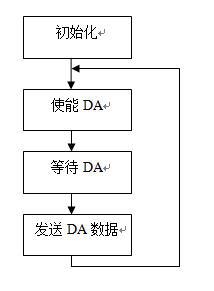

2.2 DA輸出

--*********************65536Hz分頻進程************************

process(clk)

variable cnt1 : integer range 0 to 762;

begin

if clkevent and clk=1 then

case cnt1 IS

WHEN 381 =>

cp_65k=1;

cnt1:=cnt1+1;

WHEN 762=>

cnt1:=0;

cp_65k=0;

cp_wr=0;

WHEN 20=>

cp_wr=1;

cnt1:=cnt1+1;

WHEN OTHERS=>

cnt1:=cnt1+1;

end case;

end if;

end process;

--*********************1kHz分頻進程************************

process(cp_65k)

variable cnt1 : integer range 0 to 64;

begin

if cp_65kevent and cp_65k=1 then

case cnt1 is

when 32=>cp_1k=1;

cnt1:=cnt1+1;

when 64=>cnt1:=0;

cp_1k=0;

when others=>cnt1:=cnt1+1;

end case;

end if;

end process;

--**************DDS地址累加器進程**********************

PROCESS(cp_65k)

BEGIN

IF(cp_65kEVENT AND cp_65k=1) THEN

--DDS累加器循環累加dds_m

IF dds_add65535 THEN

dds_add=dds_add+dds_m;

ELSE

dds_add=dds_add+dds_m-65536;

END IF;

END IF;

END PROCESS;

--***********************頻率加減控制進程***************************

process(cp_1k)

VARIABLE keys:INTEGER RANGE 0 TO 127 :=0; --消抖累加器

begin

if cp_1k=1 then

case key is

when 10=> --頻率加

if keys=127 then

keys:=0;

bell=1;

if dds_m=1000 then

dds_m=1;

else

dds_m=dds_m+1;

end if;

else

keys:=keys+1;

end if;

when 01=> --頻率減

if keys=127 then

keys:=0;

bell=1;

if dds_m=1000 then

dds_m=1;

else

dds_m=dds_m-1;

end if;

else

keys:=keys+1;

end if;

when others=>bell=0;

end case;

end if;

end process;

end dac;

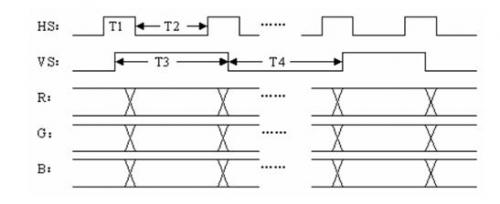

2.3 VGA顯示

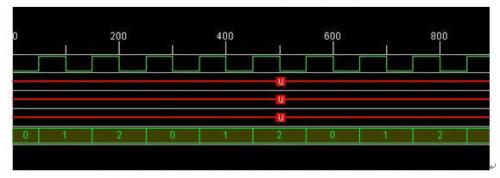

3.性能指標

DA輸出的波形

4.總結

經過了多日的努力,我們在本設計中基本實現了上述要求,并在有些功能方面提出了改進,使系統設計更加完善。在該設計中我們使用了FPGA作為主控器,但由于時間及器材條件的限制,本設計也存在不足,例如,測量范圍不能達到更高的要求,測量精度也存在很大的提升空間。我們會在以后的學習中不斷地彌補這些不足,完善測量系統設計。

評論