基于FPGA的電子表決器電路的設計與實現

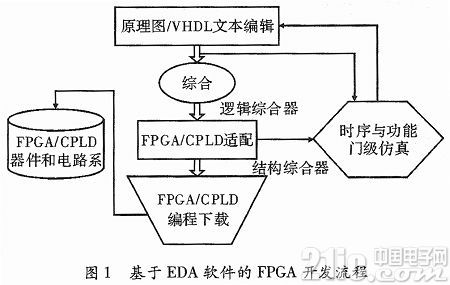

電子設計自動化(Electronic Design Automation,EDA)是以計算機為載體,在EDA軟件平臺上,用硬件描述語言VHDL完成設計文件,然后由計算機自動地完成邏輯編譯、化簡、分割、綜合、優化、布局、布線和仿真,直至對于特定目標芯片的適配編譯、邏輯映射和編程下載等工作。EDA技術的出現,大幅提高了電路設計的效率和可操作性,減輕了勞動強度。利用EDA工具,電子設計師可從概念、算法、協議等方面開始設計電子系統,大量工作可通過計算機完成,并可將電子產品從電路設計、性能分析到設計出PCB版圖的整個過程都在計算機上自動處理完成。基于EDA軟件的FPGA開發已廣泛應用于電子電路的設計與實現中,圖1為基于EDA軟件的FPGA開發流程。

本文引用地址:http://www.czjhyjcfj.com/article/201610/308318.htm

1 電子表決器電路

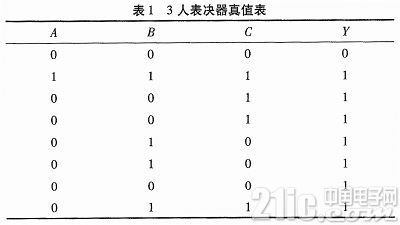

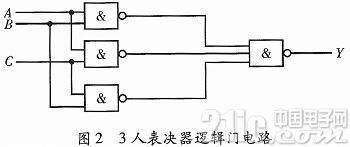

傳統的電子表決器通過邏輯門電路實現、功能簡單、不易擴展,表1是一種3人表決器的真值表,圖2是由邏輯門組成的電路圖。

2 基于FPGA的電子表決器

2.1 8人表決器電路

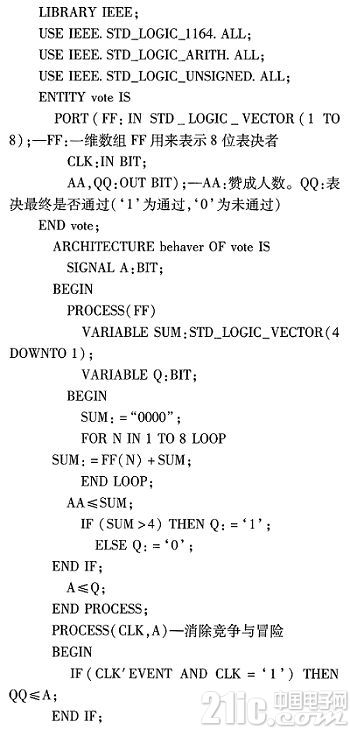

結合VHDL語言在FPGA平臺實現電子表決器電路設計,可減小系統面積,方便擴展升級,以下程序是使用VHDL語言描述的8人表決電路。

2.2 10人表決器電路

通過8人表決電路表決通過時電路狀態的觀察和驗證,使用VHDL語言在FPGA平臺實現10人表決器電路設計。在8人表決器編程基礎上修改程序,實現10人表決器電路的設計。編程中完成參與表決的每個人均可選擇贊成、放棄或棄權。同時,增加了控制鍵,可增加專人在進行表決過程中的控制,實現了表決的開始、結束和數據的鎖存。

3 電路仿真

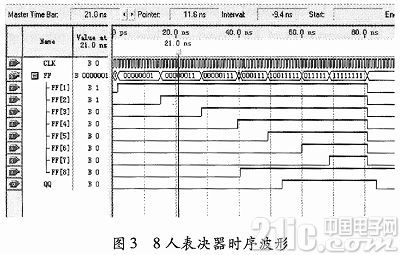

圖3是8人表決器電路時序波形,從圖中可看出程序實現了設計要求,在8人表決器程序的RTL生成電路界面顯示有9個邏輯門和硬件資源組成電路。

按圖4所示進行管腳鎖定后,即可在實驗箱上進行驗證,將程序下載到實驗平臺后,獲取實驗結果,經驗證符合設計要求。

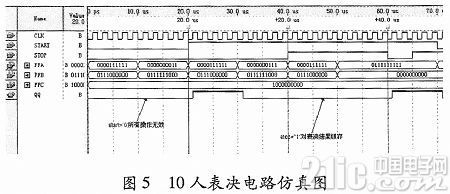

圖5為程序仿真結果。在10人表決器的RTL電路界面圖中可看出,其比8人表決器程序的RTL電路界面圖多出了一些硬件資源,若單獨使用邏輯門設計電路將是一件復雜的工作,且不便于修改和測試。

而使用EDA進行設計,還可方便地進行系統擴展,如上述程序中只需增加幾個輸出端口,將SUMA,SUMB,SUMC的值賦給相應端口,在外接數碼管便可顯示出贊成、反對、棄權的人數。或增加聲音模塊,使系統更具實用價值。而進行這些工作只需改變程序,加入現成的元器件即可。

4 結束語

電子表決器,做為投票系統中的客戶端,是一種代表投票或舉手表決的裝置。基于FPGA電子表決器的設計解決了傳統投票表決方式存在投票耗時長、計票任務重,且易于出錯、易受人控制等缺點,故在表決、選舉中獲得了廣泛應用。

評論