基于FPGA非正弦波形發生器的電路設計

摘要:文中提出了一種基于FPGA中LPM(Library Parameterized Modules)的非正弦波形發生器的電路設計方案,并完成系統的軟硬件設計。該系統的硬件部分主要用來生成和輸出非正弦波形信號,由3.3 V和正負5 V電源模塊,DA9708芯片、截止頻率為1kHz的二階低通濾波器、正負5 V的幅度調節器構成。軟件部分采用QuartusII進行硬件描述語言進行編程,在MATLAB中生成非正弦波形數據。通過MATLAB仿真與實驗輸出波形對比表明,該非正弦波形發生器的設計實現周期短、輸出非正弦波形平滑穩定,達到設計要求。

本文引用地址:http://www.czjhyjcfj.com/article/201610/307231.htm隨著直流輸電技術的應用發展,高壓電纜線路和補償電容的增多,電力系統中的諧波分量將大大增加,它給電力設備和弱電系統帶來了諧波污染,并且電力電子裝置的日益增多,使電網中的高次諧波愈來愈嚴重。因此,檢驗諧波控制設備的性能,或者測試負載設備在收到擾動時的工作情況等,需要一些專門的諧波發生器來產生所需的諧波。目前設計信號波形發生器的方法主要有3種:傳統的直接頻率合成技能(DS),鎖相環式頻率合成器(PLL),直接數字式合成器(DDS)。文獻中設計了基于FPGA LPM多功能信號發生器,其產生的波形為鋸齒波,三角波,階梯波和方波等規則波形,其波形數據采用數據表格輸入,對于復雜的畸變波形信號的產生有很大的局限性。

以上信號發生器和一些常用的函數發生器都只能產生常用的正弦波、方波和鋸齒波等常規波形,作為電路的激勵源,能滿足一般的實驗和研究的需要,不能滿足檢驗諧波控制設備的需要,因此文中提出了一種基于FPGA中LPM的畸變波形發生器的電路設計。該系統對保證今后電力系統諧波的檢測與研究,具有十分重要的技術意義和經濟價值。

1 電路設計原理

LPM是FPGA中的參數可設置模塊庫,Altera提供的可參數化宏功能模塊是基于Altera器件的結構做了優化設計。QuartusII中含有功能強大的LPM_ROM模塊。在波形發生器的設計中,在ROM中儲存有數據,改變地址,就可以讀出對應地址的數據,改變地址的變化頻率,通過建立參數化的 LPM_ROM并存入所需要額波形數據并進行驗證。

圖1所示的畸變波形發生器的結構由4個部分組成:FPGA模塊、8位DA芯片、二階低通濾波器、幅度調節器。FPGA采用EP4CE30F23C8N,頂層singal.vhdl在FPGA中實現,包含2個部分:一是ROM的地址信號發生器,由6位計數器擔任;二是一個諧波信號數據ROM,由 LPM_ROM模塊構成。LPM_ROM底層是FPGA中的EAB、ESB或M4K等模塊。地址發生器的時鐘CLK的輸入頻率f0與每周期的波形數據點數 (選擇512點)得出D/A輸出的頻率f的關系是:

2 系統硬件設計

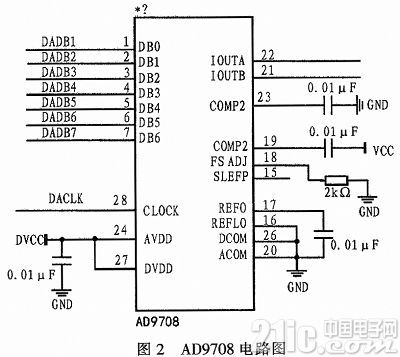

模擬輸出硬件電路圖如圖2和圖3所示。

該模擬端硬件電路由電源模塊,高速DA9708芯片、截止頻率為1 kHz的二階低通濾波器、正負5 V的幅度調節電路構成。DA9708采用單電源供電的低功耗電流輸出型高速數模轉換器,轉換速度高達125MSPS,建立時間不大于35 ns,轉換精度為1/4LSB,內置1.2 V參考電壓,輸出端采用查分電流輸出。

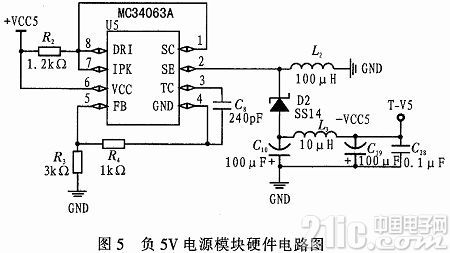

3.3 V和負5 V電源模塊如圖4和圖5所示,其分別采用LM1117和MC34063電源芯片,LM1117提供電流限制和熱保護,芯片電路包含1個齊納調節的帶隙參考電壓以確保輸出電壓的精度在±1%以內,輸出端需要一個至少10μF的鉭電容可以改善瞬態響應和穩定性。

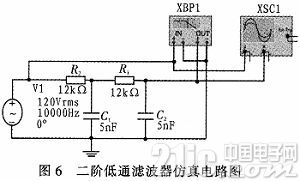

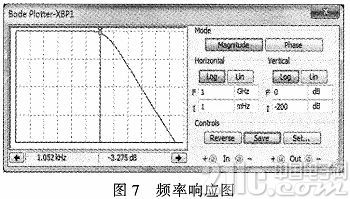

AD9708芯片差分輸出以后,為了防止噪聲干擾,電路中接入了二階低通濾波器,截止頻率為1 kHz,其Multisium仿真電路如圖6所示。

頻率響應如圖7所示,由圖7可知,其截止頻率為1 kHz。

濾波器之后,使用了2片高性能145MHz帶寬的運放AD8065,實現差分變單端,以及幅度調節功能,是整個電路性能得到而最大限度的提升。幅度調節,使用的是5K的電位器,最終的輸出范圍-5~5 V(10 Vpp)。

3 系統軟件設計

3.1 系統軟件結構設計

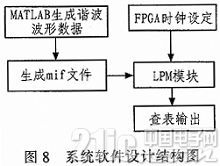

系統軟件設計結構圖如圖8所示。

在軟件設計中,由MATLAB生成畸變波形數據,在文檔編輯器中生成LPM可識別的mif文件,然后導入LPM模塊,在FPGA運行過程中,時鐘設定為40 MHz,并且對LPM模塊進行查表法輸出。

3.2 MATLAB生成諧波波形數據文件

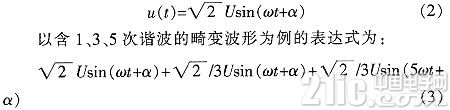

電網穩態的供電電壓波形為工頻正弦波形,數學表達式為:

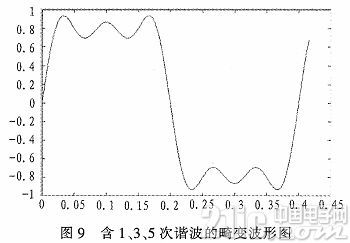

Usin(ωt+α)項稱為基波,其周期與原畸變波形的周期相同,其它各相均為諧波。由于諧波的頻率是基波頻率的整數倍,所以Usin(3wt+α)項稱為三次諧波,Usin(5wt+α)項稱為五次諧波。在matlab仿真中的含1,3,5次諧波的畸變波形如圖9所示,并產生畸變波形數據。

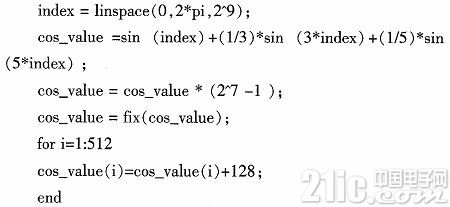

Matlab生成波形數據的部分程序為:

3.3 定制LPM_ROM初始化數據文件

QuartuslI能接受的LPM_ROM中的初始化數據文件的格式有2種:Memory Initialization File(.mif)格式和Hexadecimal(Intel-Format)File(.hex)格式,利用QuartusII的Text File編輯,以后綴名mif格式存盤,便可得到Memory Initializationg File格式的文件。本設計采用512點諧波波形數據,將MATLAB生成的512點波形數據導入QuartusII中。

生成mif文件的部分程序為:

WIDTH=8;

DEPTH=512;

ADDRESS_RADIX=UNS;

DATA_RADIX=UNS;

CONTENT BEGIN

0:80;

1:82;

2:84;

3:86;

…(數據略去)

END;

4 實驗對比

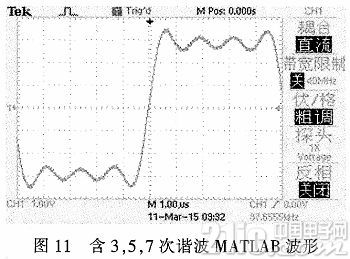

對設計好的電路板進行編程后,通過FPGA板中JTAG仿真器把程序加載到系統中運行,用TEK示波器進行測量得出了具體變波形圖,圖 10和圖11列出了含3,5,7次諧波的畸變波形信號,并通過MATLAB仿真與輸出波形進行了對比,其中,左側為示波器實際測量波形,右側為 MATLAB仿真波形。

5 結論

該系統采用MATLAB生成畸變波形數據以及基于FPGA中的LPM模塊系統對波形數據進行處理,最后通過硬件電路對數字信號進行模擬轉換輸出,通過對比實驗波形和MATLAB仿真波形,得出了系統產生的波形具有了諧波信號的特征,并且輸出波形平滑穩定,沒有雜波,可以用于檢測諧波控制設備的性能,極大縮短了畸變波形發生器開發的周期,具有很好的應用前景。

評論