串行外設接口(SPI)總線時序詳解

SPI,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節約了芯片的管腳,同時為PCB的布局上節省空間,提供方便,正是出于這種簡單易用的特性,現在越來越多的芯片集成了這種通信協議。SPI是一個環形總線結構,由ss(cs)、sck、sdi、sdo構成,其時序其實很簡單,主要是在sck的控制下,兩個雙向移位寄存器進行數據交換。

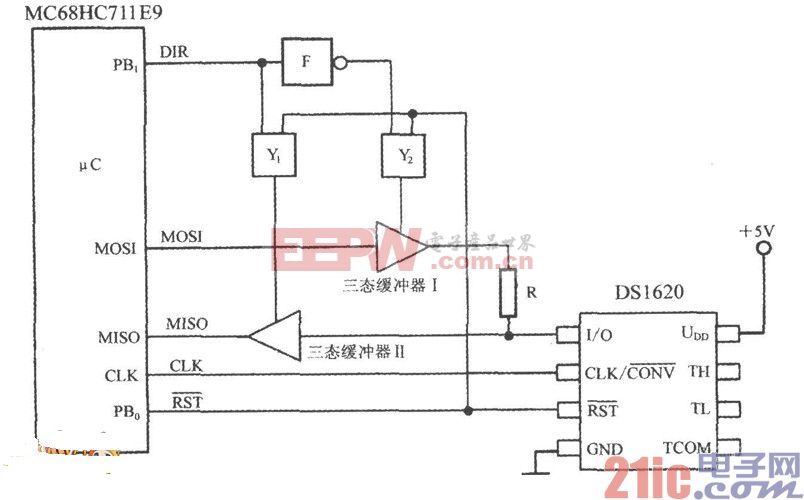

本文引用地址:http://www.czjhyjcfj.com/article/201609/303467.htmSPI總線是Motorola公司推出的三線同步接口,同步串行3線方式進行通信:一條時鐘線SCK,一條數據輸入線MOSI,一條數據輸出線 MISO;用于 CPU與各種外圍器件進行全雙工、同步串行通訊。SPI主要特點有:可以同時發出和接收串行數據;可以當作主機或從機工作;提供頻率可編程時鐘;發送結束中斷標志;寫沖突保護;總線競爭保護等。

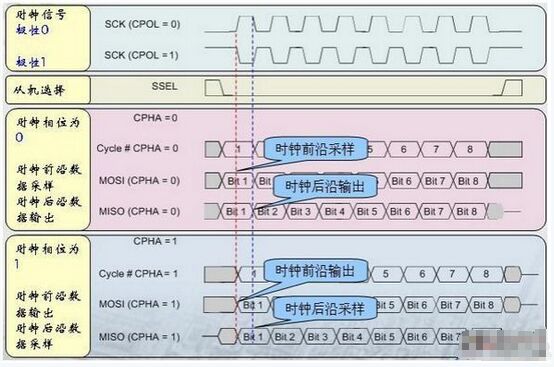

SPI總線有四種工作方式(SP0, SP1, SP2, SP3),其中使用的最為廣泛的是SPI0和SPI3方式。SPI模塊為了和外設進行數據交換,根據外設工作要求,其輸出串行同步時鐘極性和相位可以進行配置,時鐘極性(CPOL)對傳輸協議沒有重大的影響。如果CPOL=0,串行同步時鐘的空閑狀態為低電平;如果CPOL=1,串行同步時鐘的空閑狀態為高電平。時鐘相位(CPHA)能夠配置用于選擇兩種不同的傳輸協議之一進行數據傳輸。如果 CPHA=0,在串行同步時鐘的第一個跳變沿(上升或下降)數據被采樣;如果CPHA=1,在串行同步時鐘的第二個跳變沿(上升或下降)數據被采樣。

SPI主模塊和與之通信的外設音時鐘相位和極性應該一致。

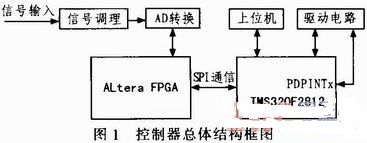

SPI時序詳解---SPI接口在模式0下輸出第一位數據的時刻SPI接口有四種不同的數據傳輸時序,取決于CPOL和CPHL這兩位的組合。圖1中表現了這四種時序,時序與CPOL、CPHL的關系也可以從圖中看出。

圖1

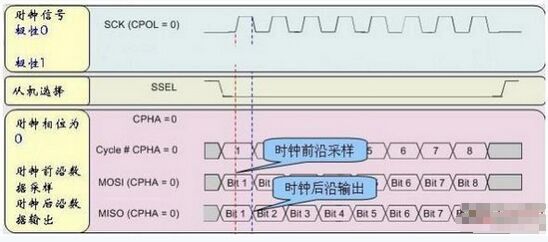

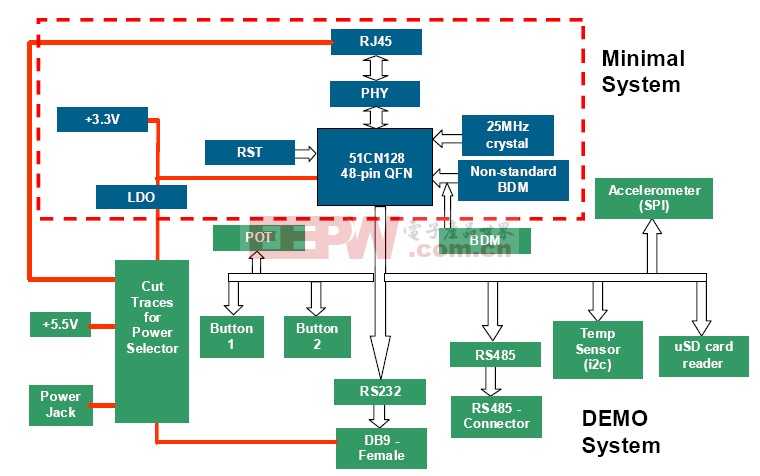

CPOL是用來決定SCK時鐘信號空閑時的電平,CPOL=0,空閑電平為低電平,CPOL=1時,空閑電平為高電平。CPHA是用來決定采樣時刻的,CPHA=0,在每個周期的第一個時鐘沿采樣,CPHA=1,在每個周期的第二個時鐘沿采樣。由于我使用的器件工作在模式0這種時序(CPOL=0,CPHA=0),所以將圖1簡化為圖2,只關注模式0的時序。

圖2

我們來關注SCK的第一個時鐘周期,在時鐘的前沿采樣數據(上升沿,第一個時鐘沿),在時鐘的后沿輸出數據(下降沿,第二個時鐘沿)。首先來看主器件,主器件的輸出口(MOSI)輸出的數據bit1,在時鐘的前沿被從器件采樣,那主器件是在何時刻輸出bit1的呢?bit1的輸出時刻實際上在 SCK信號有效以前,比SCK的上升沿還要早半個時鐘周期。bit1的輸出時刻與SSEL信號沒有關系。再來看從器件,主器件的輸入口MISO同樣是在時鐘的前沿采樣從器件輸出的bit1的,那從器件又是在何時刻輸出bit1的呢。從器件是在SSEL信號有效后,立即輸出bit1,盡管此時SCK信號還沒有起效。

從這張圖就可以很清楚的看出主從器件的bit1是怎樣輸出的。

評論