恒比定時甄別器(CFD)電路具體實現探討

介紹PET系統中定時方法時有介紹到目前大部分使用到的是CFD方法,CFD是Constant Fraction Discriminator的縮寫。

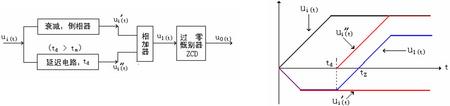

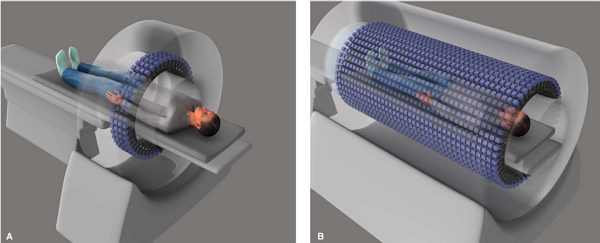

本文引用地址:http://www.czjhyjcfj.com/article/201602/287342.htm這里對CFD具體方法概念,不再贅述,本文筆者個人帶著學習的態度來給大家介紹下該方法電路的具體實現。為了介紹方便,我們還是將CFD的實現框圖擺出來,如圖1所示。

圖1:CFD原理框圖

因為需要精確定時,所以在前面博文中,筆者詳細介紹了,當圖1中的輸入信號的幅度不同時,如果采用雙閾值檢測,那么會出現時間晃動,在上述鏈接博文的圖2和圖3有非常形象的展示。

而上述圖1就可以非常理想的避免這個問題,我們看到不管輸入信號的幅度怎么變化,圖1右側的tz時刻(即過零時刻)都會保持固定,這就是我們所需要的,即每次hit我們都能進行精確的定時。(這里,大家一定要看懂右側圖,首先輸入信號為黑線,上面紅線表示經過延遲后的輸入,下面紅線是經過衰減并倒相的輸入,最后藍線就是上述二者相加得到的結果,藍線和橫軸相交產生了過零點)

有了這原理框圖,那么剩下的就是具體實現,圖1左側中,分別有衰減、倒相、延遲、加法器以及過零檢測等主要電路模塊,后面我們將對它們一一進行詳細的具體實現介紹。

雙極性信號成形方法

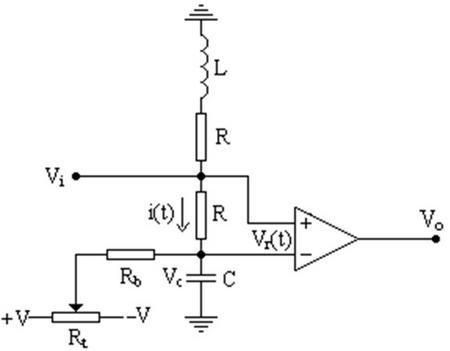

如圖2所示,輸入信號Vi直接連到比較器的同相輸入端,比較器的反相輸入端信號Vc是Vi的低通濾波輸出,它在時間上比輸入信號滯后。比較器的同相、反相輸入端之間的電壓差為:

Vr(t)=Vi(t)-Vc(t)=R*i(t)=RCdVc(t)/dt

圖2:雙極性成形電路

在電容器上的電壓達到峰值之后,積分電阻上的電流方向改變,引起比較器輸出翻轉。由于電阻電容組成的是一個線性網絡,Vr(t)的過零與輸入信號的幅度無關,從而實現了恒比定時功能。

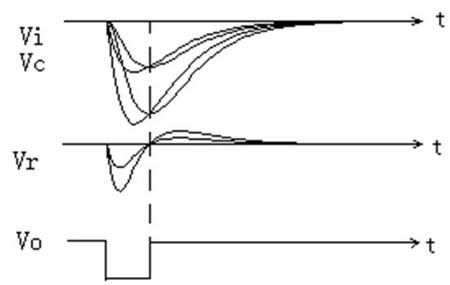

圖3:CFD輸出

注:圖1中反相可以通過圖2中的放大器實現一個減法器來實現;而RC濾波器來實現一個延時,這樣在整個CFD電路中就實現了所謂的無延遲線的CFD。

評論