汽車顯示器接口設計關鍵技術分析

IMS Research的調查顯示,帶有視頻功能的汽車音響主機的數量將會由2006年的850萬臺增長到2015年的2660萬臺。為了既能向駕駛員提供信息,又不分散其注意力,顯示器需要安裝在遠離汽車音響主機的位置,并將畫面投影到擋風玻璃的背面。這種結合了圖像源和面板的視頻接口正在越來越多地從模擬視頻技術轉向質量更高的RGB(紅綠藍)數字視頻格式,后者已成為LCD顯示器中使用的標準接口。前端顯示應用的電纜長度通常保持在1到3米的范圍內,而后座娛樂(RSE)單元的電纜則需要達到8米甚至更長。這種連接支持千兆位/秒的數據傳輸速率,遠超過傳統車載網絡的波特率,并可以利用點對點串行器/解串器(SerDes)解決方案完美實現。與傳輸一路較寬的并行視頻總線相比,這種芯片組大大降低了傳輸線和連接器的引腳數量,從而實現了出眾的系統級優勢。

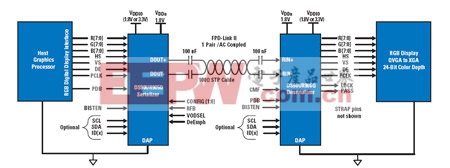

本文引用地址:http://www.czjhyjcfj.com/article/197572.htm為滿足汽車顯示器接口方面的嚴苛要求,比如高數據吞吐量、超薄布線、高級信號調節、可檢測性以及超低EMI(電磁干擾)等。美國國家半導體(NS)公司開發出DS90UR905/6 和DS90UR907/8 SerDes芯片組,該產品是能將分辨率從QVGA(400 x 240)擴展到24位色深的XGA(1024 x 768)的嵌入式時鐘SerDes解決方案。寬范圍的像素時鐘頻率使汽車制造商只需在其整個車型系列中采用一個數字視頻顯示接口方案,即可覆蓋從雙畫面的小儀表盤面板、中控臺的LCD到更大尺寸的RSE顯示器應用。

視頻應用和SerDes概念

SerDes組件的目標應用領域是平板顯示器鏈路接口,它可以通過一根較長的串行電纜把圖像主機與顯示器連接起來。典型的例子包括:中央信息顯示器(CID)、儀表盤、頭枕上的娛樂顯示器或為后座乘客準備的車頂下降式顯示模塊,如圖1所示。這些新型芯片組是NS推出的FPD-Link II系列產品中的一組,它們可以將一個視頻源的27位數字RGB色彩信息和時間控制信號轉換成一個嵌入了時鐘信息的單一串行數據流在雙絞線上傳輸。芯片組在I/O(輸入/輸出)層采用高速的差分信號,也就是說,在真(正)端子上傳輸實際信號的同時,互補(負)端子上傳輸與之對應的相反極性信號。

圖2在系統層面上描述了視頻傳輸的概念。除了顏色和時序位外,還有一個可選的I2C控制接口,它可替代通過常規引腳帶選項實現的組件配置。芯片組支持18bpp(每像素位)或24bpp的色深。彩色顯示器使用3個子像素(紅、綠、藍)來定義一個單獨的像素。由于每個像素有18位(6位紅,6位綠和6位藍),我們可以得到26.2萬種顏色。大多數人的眼睛可以看到1000萬種以上的顏色,這也就解釋了為什么使用24bpp已成為趨勢:它能提供超過1600萬種顏色,可實現更豐富的用戶體驗和平滑的顏色梯度。像素時鐘范圍現已極寬:頻率可從5MHz 到65MHz,這使得串行鏈路速率從140Mbps提高到1.82Gbps,涵蓋了汽車顯示器的全部主流分辨率。

并行LVCMOS輸入和輸出信號可以分別靈活地對準同步發射器輸入及接收器恢復輸出時鐘(PCLK)的上升沿或下降沿,這一特性大大簡化了串行器至圖像控制器以及解串器至LCD計時控制器的接口連接。在發射器并行時鐘周圍的一定頻段內,SerDes芯片組在預同步接收器的PLL時無需外部參考時鐘(石英或振蕩器)。甚至在一切可能的隨機數據模式傳輸過程中該同步都能得到保證,這被稱為隨機數據鎖定特性。這不僅節省了參考組件系統的成本,而且消除了另一個潛在的電磁干擾源。該性能還可以實現熱插拔,即在不需要任何特殊排序或訓練模式的情況下,就可以對送往解串器的串行數據流執行斷言/取消斷言操作。

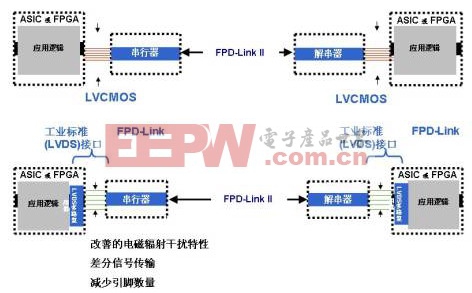

一旦接收器PLL鎖定在發射器的頻率下,即可由LOCK輸出標志引腳顯示這一狀態,確保接收器輸出的數據完整性。DS90UR907/8芯片組具有DS90UR905/6芯片組的一切特性,兩耳區別在于輸入輸出不再是發送LVCMOS信號的并行總線,而是遵照開放的工業標準FPD-Link。很多現代化的圖像控制器、顯示定時控制器、ASIC和FPGA都支持這種一級串行化技術,它采用適合18bpp的3個數據通道,或者適合24bpp的4個數據通道,每一個都有一路并行時鐘通道。電信號的發送遵循開放的ANSI/TIA/EIA-644A標準,該標準又稱作LVDS(低壓差分信號傳輸)。使用該接口技術代替常規LVCMOS的優勢在于:采用差分信號可降低電磁干擾,并減少組件的引腳數量,如圖3所示。

圖3 FPD-Link系統接口選項的優勢

評論