嵌入式脈象采集儀電路設計

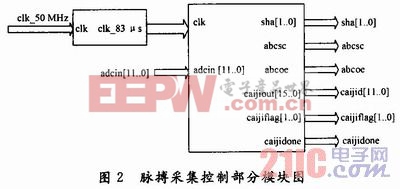

完整編譯綜合采集部分后由兩部分組成,如圖2所示。

3.2 基于NiosⅡ的SoPC硬件設計

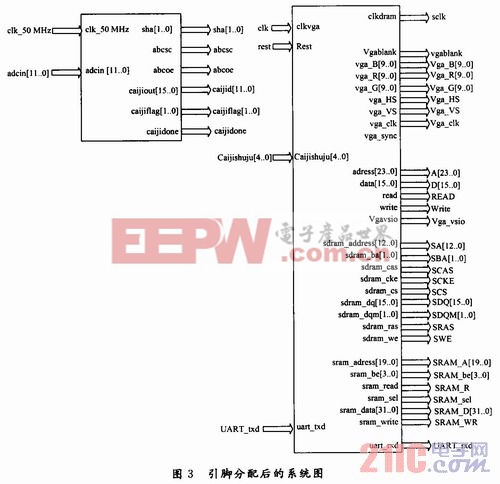

利用Altera公司的QuartusⅡ軟件和SoPCBuilder開發工具,可以方便地定制一個從硬件到軟件的完整系統。FPGA內部需要設計以下模塊:NiosⅡ、SRAM控制器、SDRAM控制器、EPCS控制器、FLASH控制器、定時器、VGA控制器、RS 232控制器、脈象采集控制器等。除脈象采集控制器沒有現成的IP核可用,需開發控制時序外,其他控制器采用Altera公司提供的IP核。

SoPC系統生成完成后,在QuartusⅡ下建立原理圖窗口,調用設計好的NiosⅡ系統與自己設計的脈象采集系統的控制連接,設計完成后,鎖定引腳,進行完整編譯。完成后的電路如圖3所示。

編譯后配置到系統中的FPGA去,后面的工作就是嵌入式操作系統的移植和嵌入式應用程序的開發,這時會利用到該硬件平臺。

4 結語

設計出嵌入式脈象采集儀的總體方案,并完成了基于FPGA的脈象采集儀硬件電路設計。根據脈象采集的特點,設計脈象采集部分電路,利用IP核構建了脈象采集的SoPC系統。設計的脈象采集儀具有成本低,功耗低,體積小,便于擴展,使用方便,穩定性高,可靠性高,系統維護方便等特點。

本文引用地址:http://www.czjhyjcfj.com/article/195166.htm linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論