Design Compiler 2010將綜合和布局及布線的生產效

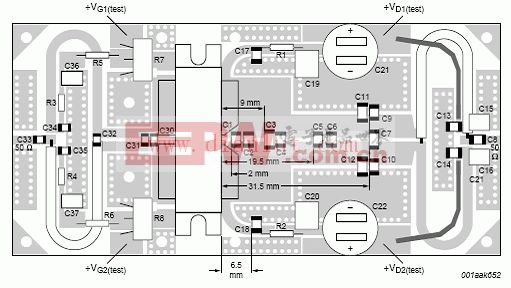

半導體設計、驗證和制造的軟件及知識產權(IP)供應商新思科技有限公司(Nasdaq:SNPS)日前宣布:該公司在其Galaxy™設計實現平臺中推出了最新的創新RTL綜合工具Design Compiler® 2010,它將綜合和物理層實現流程增速了兩倍。為了滿足日益復雜的設計中極具挑戰性的進度要求,工程師們需要一種RTL綜合解決方案,使他們盡量減少重復工作并加速物理實現進程。為了應對這些挑戰,Design Compiler 2010對拓撲技術進行擴展,為Synopsys旗艦布局布線解決方案IC Compiler提供“物理層指引”;將時序和面積的一致性提升至5%的同時,還將IC Complier的布線速度提升了1.5倍。Design Compiler 2010的這一項新功能使RTL工程師們能夠在綜合環境中進行布局檢測,從而可以更快地達到最佳布局效果。此外,Design Complier采用可調至多核處理器的全新可擴展基礎架構,在四核平臺上可產生兩倍提升綜合運行時間。

本文引用地址:http://www.czjhyjcfj.com/article/193819.htm“縮短設計時間和提升設計性能是確保我們市場競爭力的關鍵。”瑞薩科技公司DFM和數字EDA技術開發部門部經理Hitoshi Sugihara說:“借助拓撲技術在物理層指引中的全新延展,我們看到了Design Compiler設計綜合器和IC Compiler芯片編譯器之間差異在5%以內的一致性,使IC Compiler上實現了高達2倍速的更快布局和更好的設計時序。我們正在采用Design Compiler中這項技術創新,將我們的重復工作降到最低,同時在更短的設計周期內達到我們的設計目標。”

評論