使用新型 Virtex FPGA 開發小型軟件無線電平臺:S

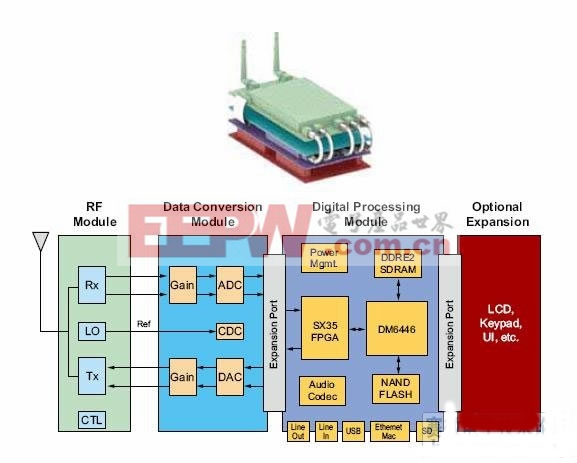

SFF SDR(小型軟件定義無線電)開發平臺是一種模塊化的 RF/IF/基帶平臺(圖 1 和圖 2)。該平臺展示了 Xilinx 和德州儀器 (Texas Instruments, TI) 的最新芯片產品以及最新高級設計流程和軟件架構。 這個平臺還為手持設備開發人員提供了特定的關鍵功能,如實時功耗配置和監測。

本文引用地址:http://www.czjhyjcfj.com/article/193341.htm

此平臺是德州儀器、Xilinx 和 Lyrtech 以及眾多主要軟件工具供應商聯合開發的成果。 此平臺具有一個 Xilinx® Virtex-4 器件,該器件的先進功能可為您開發高效的功耗優化設計助一臂之力。

本文將討論組合 DSP/FPGA 架構和設計的趨勢及其在 SFF SDR 開發平臺中體現的方法。 本文還將介紹用混合設計流程(對于 FPGA 使用基于模型的開發方法,對于片上系統的 DSP 使用 C/匯編語言)設計的簡單的家用無線電服務 (FRS) FM 調制方法和較復雜的 GSM 調制方法。

圖 2 – SFF SDR 開發平臺的框圖與技術

SFF SDR 開發平臺

SFF SDR 開發平臺提供從天線到基帶處理的完整信號鏈。 可以用這套系統為軍事、公安和商業應用創建單協議或多協議無線電手持設備。 這套系統還可用作快速原型設計和測試平臺。 另外,該平臺為了與 The MathWorks 的 Simulink 基于模型的設計 (MBD) 工具一起使用而進行了集成,所以可以選擇使用 C/HDL 或 MATLAB Simulink 快速測試概念驗證設計以及對架構進行成本和功耗優化。

與市場上其他 SDR 開發產品不同,SDR 開發平臺是軟硬件共同開發環境,可為多協議 SDR 設備提供全套構件,包括 RF 前端模塊、模數及數模數據轉換模塊和數字處理模塊。 通過將基帶、IF 和 RF 分割成分立模塊而非采用單一混合架構,就可以用替換己方或第三方模塊的方法增強您的無線電開發能力,并進行成本和功耗優化。 這一靈活性至關重要,因為它使您有能力針對日新月異的行業要求調整自己的產品。

基帶模塊具有一個 Xilinx Virtex-4 SX35 FPGA 和一個 TI TMS320DM6446 芯片。 TI 芯片包含一個 TMS320CC64x+ DSP 內核和一個 ARM9 通用處理器內核。 SDR 開發平臺具有一個獨特的功耗測量 API。 此 API 可測量 FPGA、DSP 和 ARM 的加載并報告實時功耗數據。 這樣,您就可以提取特定數據速率下的突發和峰值功耗等重要信息,從而準確地估計電池壽命。 您還可以快速估計不同系統配置的功耗影響。 例如,您可以嘗試在 FPGA 和 DSP 之間進行不同的系統功能分配,以獲得最佳的功耗/性能平衡。

FRS 和 GSM 應用示例

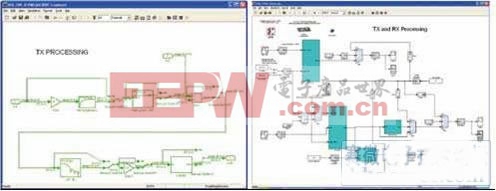

SFF SDR 開發平臺包含一個基本應用示例: 簡單的 FRS FM 波形。 圖 3 所示示例完全采用基于模型的方法設計,以便顯示該平臺的快速原型設計功能。 此應用還說明了如何在 DSP 和 FPGA 之間分配應用功能,并且說明了將不同處理部分從 FPGA “轉移”到 DSP(以及相反過程)的效果。

( a) (b)

圖 3 – 用“完全基于模型設計”的方法設計簡單的 FRS 波形。 圖 3(a) 所示為 DSP 處理(Tx 端);圖 3(b) 所示為 FPGA 處理(Rx 和 Tx 端)。

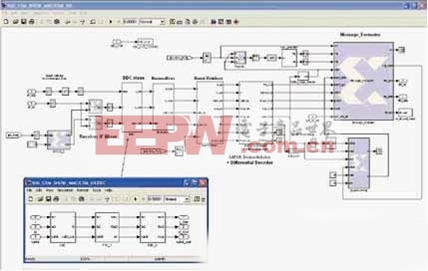

圖 4 所示為使用 Simulink/Xilinx System Generator for DSP 中基于模型的方法實現的 GSM 物理層的 FPGA 部分。 此模型實際上是一個可執行的框圖,其中所有信號處理功能都可以通過結合 Simulink 信號源、信道仿真、輸出示波器和數據誤碼率分析進行仿真和驗證。

這一方法的優點是,一旦完成仿真,即可將模型綜合到 FPGA 比特流中去用實際信號執行。

我們先淺釋開發過程,然后對非常具體的 DSP 相關實現和時序實現方面進行較深入的探討。

該 GSM 項目當初的目標器件是 Virtex-II 系列,用一個 Virtex-4 器件對同樣的 System Generator 模塊進行了重新綜合和重新驗證。 可見采用基于模型的方法的最主要好處就是 便于器件重定向。

圖 4 – GSM 物理層的 FPGA 模型

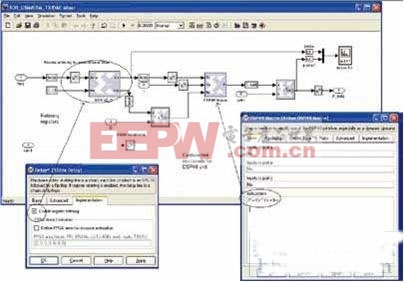

這種重定向的實現方法尚可通過第一關,但是,使用 Virtex-4 FPGA 中 DSP48 處理單元的更高級功能是為了優化設計,因為優化設計越多功耗就越小。 圖 5 所示為模型的一個關鍵的高速部件——發送端 IF 混頻器,其運行速度是 I

F 采集速度 (104 MHz)。 優化這一部分是降低功耗的關鍵。 這是通過“調整”DSP48 微碼(如圖形用戶界面子窗口中所示)實現的,該微碼被編程為執行一個乘加指令。 這樣,與 Virtex-II 器件相比,FPGA 資源就會低得多。 由于這一優化,用電量(用此平臺的功耗測量功能驗證)也會低許多,Virtex-4 器件的整體功耗配置也會得到改善。

圖 5 還顯示了 System Generator 另一個令人非常感興趣的優化功能——重定時功能。 這一強大功能使 System Generator 可以在整條流水線的適當位置插入鎖存器。 這一自動重新定時功能確實起到了簡化作用,特別是對直接數字合成 (DDS) 功能等高速部分。

Virtex-4 架構和工具的使用使 GSM 物理層的實現大受裨益。 就 FPGA 的資源和功耗而言,我們用 SFF 的功耗測量功能大大優化了實現過程。 連續功耗監測等其他功能將使您能夠對運算過程中的用電量進行表征,從而進一步實現處理優化。

圖 5 – 使用微碼自定義 DSP48 處理單元

結論

SFF SDR 開發平臺為手持設備開發人員提供了非常靈活的平臺。 此平臺以 TI 和 Xilinx 等芯片供應商提供的高級處理器以及 The MathWorks 等主要供應商提供的軟件工具為依托,為手持設備開發人員提供了一個真正的“樂高模塊箱”,在不斷加速、競爭激烈而又極有前途的無線設備市場中構建出先進的產品。

評論