基于FPGA的數(shù)字解擴解調模塊設計及實現(xiàn)

1引 言

本文引用地址:http://www.czjhyjcfj.com/article/192157.htm擴頻通信系統(tǒng)是將基帶信號的頻譜擴展到很寬的頻帶上,然后進行傳輸,通過增大頻帶寬度來提高信噪比的一種系統(tǒng)。由于擴頻系統(tǒng)具有抗干擾能力強、保密性高、截獲概率低、多址復用和任意選址等優(yōu)點,在移動通信等諸多領域越來越受到重視。

在擴頻通信系統(tǒng)中,載波同步是擴頻接收機正常解調的前提,是擴頻通信中的一項關鍵性技術。常用的載波同步技術有平方環(huán)、Costas環(huán)和通用載波恢復環(huán)等。其中Costas環(huán)是跟蹤低信噪比的抑制載波信號的最佳裝置,也是現(xiàn)實中應用最多的一種。過去擴頻信號載波同步常采用模擬Costas環(huán),但是模擬環(huán)常存在I,Q通道間幅相不平衡、必須初始校準等問題。采用全數(shù)字實現(xiàn)的環(huán)路能夠有效地避免這些問題。 本文介紹一種全數(shù)字Costas環(huán),他能夠很好地完成由BPSK調制的擴頻信號的載波同步和跟蹤,從而完成對調制信息的解擴解調。該電路具有可靠性高、體積小、功耗低、調試方便等優(yōu)點。通過編程、綜合和仿真,最后在FPGA上硬件實現(xiàn)本模塊。測試結果表明,本模塊的各項指標均達到設計要求。

2數(shù)字Costas環(huán)的基本原理

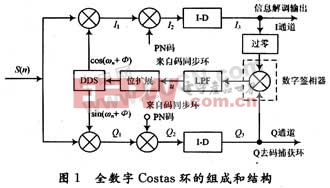

Costas環(huán)主要由數(shù)字下變頻器、解擴單元、積分-清零器(I-D)、數(shù)字鑒相器、數(shù)字環(huán)路濾波器(LPF)以及數(shù)字控制振蕩器(DDS)等模塊組成。

當輸入信號中擴頻碼(PN碼)和來自碼同步環(huán)的擴頻碼精確同步的情況下,輸入信號通過解擴單元就可以去除擴頻碼,解擴后I,Q兩路輸出分別為:

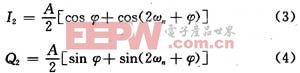

當輸入信號中擴頻碼(PN碼)和來自碼同步環(huán)的擴頻碼精確同步的情況下,輸入信號通過解擴單元就可以去除擴頻碼,解擴后I,Q兩路輸出分別為

最后通過低通濾波器濾去二倍頻,最終I,Q兩路輸出分別為:

可見,兩路乘法器的輸出均包含有調制信號,兩者相乘可消除調制信號的影響,再經(jīng)環(huán)路濾波器濾波后可得DDS控制電壓:

由于DDS的控制電壓已經(jīng)去除了基帶信號的成分,只受到相位誤差φ的控制(k為常數(shù)),所以可以對DDS進行準確的調整,實現(xiàn)對載波的精確同步和跟蹤。

3數(shù)字Costas環(huán)各子模塊設計

在作者所參與的項目中,系統(tǒng)時鐘fclk=48.96 MHz,載波頻率為(12.24 M±1.5 k)Hz,數(shù)據(jù)速率fd=16 kb/s,A/D采樣位數(shù)為8位。

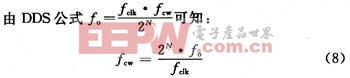

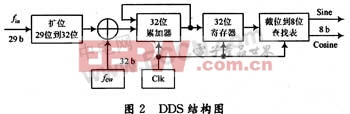

3.1 DDS模塊

輸人時鐘:fclk=48.96 MHz;輸出正弦:fo=12.24 MHz;DDS的位數(shù):N=32 b。

從資源消耗和精度的綜合考慮,采用了8位的查找表(IP核)來生成正弦余弦波,所以從累加器輸出的相位信號必須截取高8位作為查找相位數(shù)據(jù)輸入到查找表,輸出正弦余弦信號也為8位。其具體實現(xiàn)結構如圖2所示。

評論