可在線升級的FPGA并行配置方法的實現

在當今變化的市場環境中,產品是否便于現場升級、便于靈活使用,已成為產品進入市場的關鍵因素。而基于 SRAM結構的 FPGA器件的出現,為系統設計者動態改變運行電路中的邏輯功能創造了條件,也為現場升級等奠定了基礎。但由于 SRAM的掉電易失性,系統每次上電時,必須重新配置數據,只有在數據配置正確的情況下系統才能正常工作。

筆者在實際項目應用中,采用 SST89V564微處理器對 FPGA進行快速高效的 PPA數據配置,不僅可以完成對 FPGA的上電啟動配置,同時利用其 IAP技術還可以在 FPGA配置完以后,通過修改微處理器中的配置數據和參數來實現系統的在線升級。

1.FPGA的 PPA配置過程

FPGA的在線配置方式一般有兩類:一是通過下載電纜由計算機直接對其進行配置;二是通過微處理器對其進行配置。前者調試時非常方便,在應用現場是很不現實的,只適合產品的調試,而一般實際產品中采用微處理器對 FPGA進行配置。

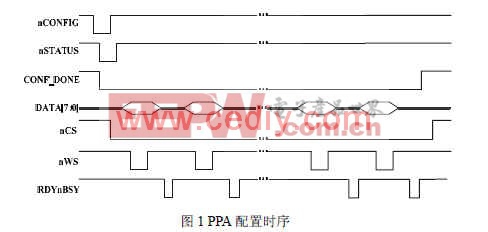

FPGA器件 PPA配置時序如圖 1所示,其中 nCS和 CS兩個片選信號只需用一個,當

選用 nCS作為片選信號控制配置,CS接高電平。其配置過程為微處理器在 nCONFIG引腳上產生一個最少 21µs的低脈沖,等待直至 nSTATUS和 CONF_DONE變低。此時將 nCONFIG置高, nSTATUS會在 nCONFIG跳高后 4µs內跳高,則表示 FPGA可以配置了[1]。

配置成功時,FPGA器件釋放 CONF_DONE信號,由外部將其拉高。如果微處理器檢

測到該信號為高,則表明配置成功;否則,要對其重新配置。

2.基本硬件組成

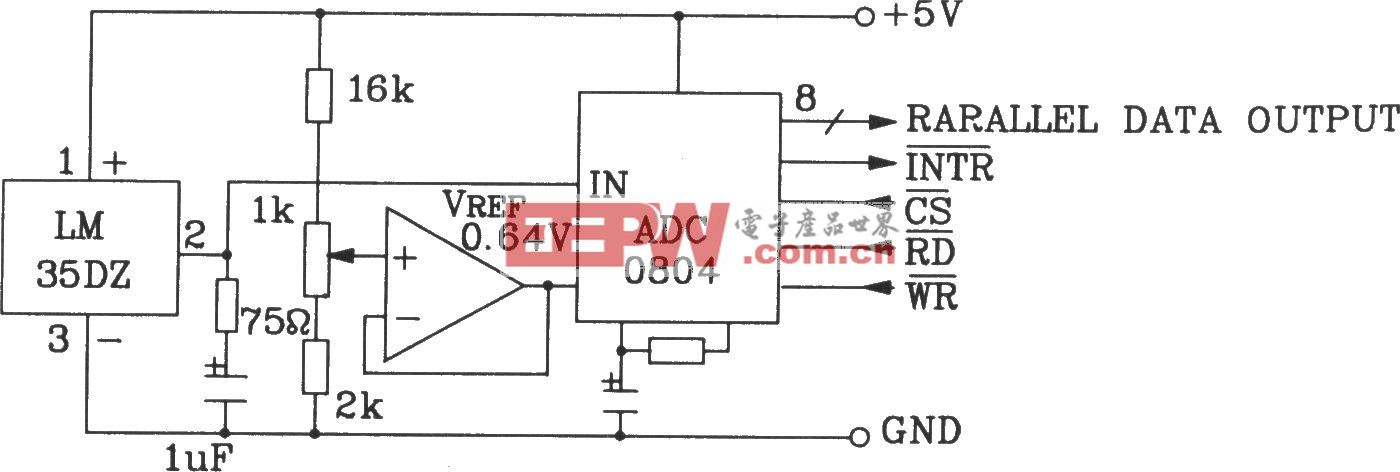

2.1 SST89V564RD及接口設計

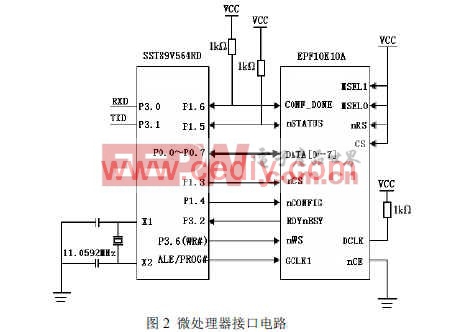

SST89V564RD是 SST公司的 8位集成 SUPERFLASH 存儲器的 51 兼容 MCU,帶有 1K字節片內 RAM和 72K字節片內 SUPERFLASH。其片內 Flash分成 Block0(64K字節)和 Block1(8K字節)兩塊,Block0和 Block1低 8K地址相同,程序運行時,可通過設置特功能寄存器 SFCF對低 8K字節的 Flash程序存儲塊進行切換,以使程序運行在 Block0或 Block1。微處理器與 FPGA的接口電路如圖 2所示。

評論