基于CPLD的電梯運行控制器的設計

4 VHDL源程序的仿真

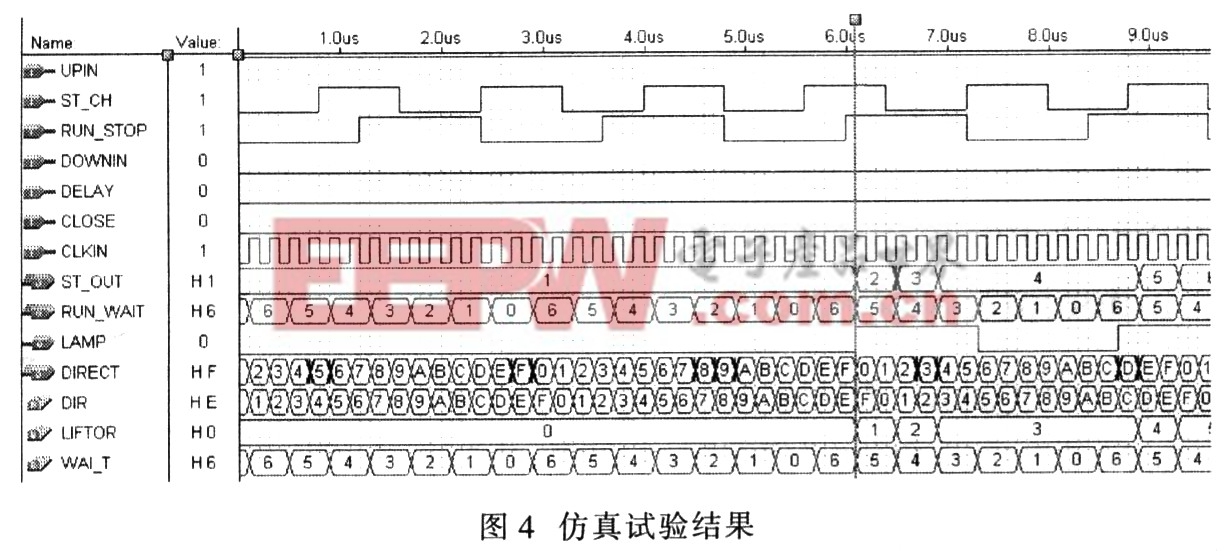

系統程序編寫完畢后,在MAX+pluslI軟件環境下對其編譯仿真。其仿真試驗結果如圖4所示。

圖4中,輸入信號為:UPIN,ST_CH,RUN_STOP,DOWNIN,DELAY,CLOSE和CLKIN;輸出信號為:ST_OUT, RUN_WAIT,LAMP,DIRECT,DIR,LIFTOR和WAI_T。當時鐘上升沿到來時,若WAI_T=0,則它的下一狀態為6;因 DELAY信號始終為低電平,故WAI_T依次自減1計數。RUN_WAIT是WAI_T和0的并置運算,故其值和WAI_T相同。

當時鐘上升沿到來時,DIR進行加1計數,且當DIR=0XF時,DIR的下一狀態值為0。與此同時,DIR加1并賦值給DIRECT。

當LAMP為低電平時,電梯處于等待狀態,故LIFTOR保持其原值不變保持0和3不變;當LAMP為高電平時,電梯處于運行狀態,因UPIN始終為高電平,DOWNIN始終為低電平,故當RUN_STOP為高電平時,電梯只能處于上升狀態,故LIFFOR進行自加1計數,同時,LIFTOR加1賦值給 ST_OUT。

5 硬件實驗

在MAx+plusII軟件編譯完后,采用EPM7128SLC84-6器件下載VHDL源程序,進行硬件試驗。

其下載步驟為:首先,指定采用可編程器件EPM7128SLC84-6;其次,依據輸入、輸出端口指定與之對應的引腳;然后,使用Pof2Jed軟件將編譯后的下載文件*.Pof。轉換成*.Jed文件;最后,使用Atmel ISP軟件將轉換后的*.Jed文件轉換成*.Chn文件。

硬件系統試驗表明,輸出信號的顯示與軟件仿真結果完全相符,達到設計要求。

6 結論

該系統軟件設計中,成功編譯并仿真VHDL源程序,且對仿真圖進行合理分析。在硬件實驗過程中,對VHDL源程序進行成功下載,所得實驗結果與軟件仿真結果完全相符,從而證明電梯運行控制器的設計滿足系統功能要求。

評論