基于FPGA的提取位同步時鐘DPLL設計

由于采用微分型超前一滯后型數字鑒相器,隨機噪聲會引起DPD的相位抖動,會生成影響DCO動作的控制脈沖,所以對于DPD輸出的Sign和Sign_ready不能作為直接驅動指導后面DCO的控制信號,DPD的濾波功能是通過一個Mod為8的計數器來實現的。當Sign_ready為1時,DPD的Mod開始加減計數(Mod復位后為8),計數的方向由Sign來控制。當Sign為1時,表示本地時鐘超前于輸入信號,Mod做加法計數,逐次加法直到15,進位變為8,Inset輸出一個1μs的高電平;同樣,當Sign為0時,表示本地時鐘超前于輸入信號,Mod做減法計數,逐次加法直到1,借位變為8,Deduct輸出一個1μs的高電平。DLF原理圖如圖4所示。本文引用地址:http://www.czjhyjcfj.com/article/191835.htm

由于噪聲和抖動一般是無序的,除非噪聲在同一方向出現8次,濾波器才會輸出誤動作。另外Clk_DLF是Clk_DPD的兩倍頻率,有助于提高濾波精度。

2.3 振蕩器結構及其實現方法

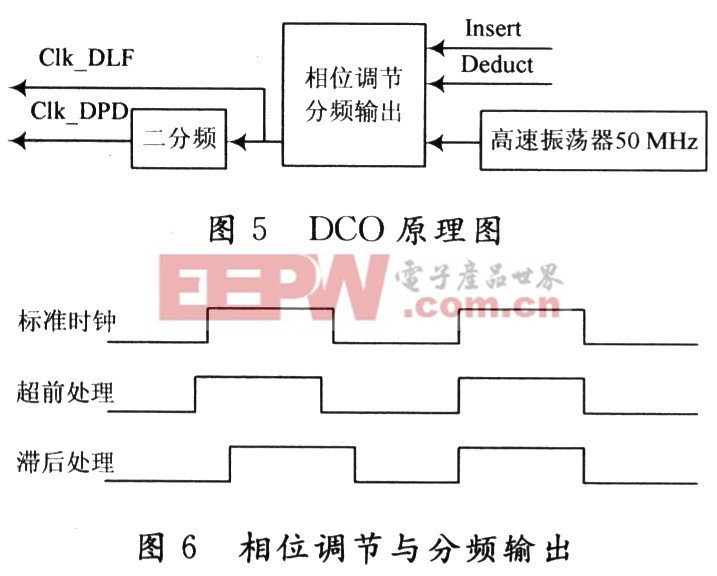

數控振蕩器,又稱為數字鐘,它在數字鎖相環路中所處的地位相當于模擬鎖相環中的電壓控制振蕩器。它的輸出是一個脈沖序列,而該輸出脈沖序列的周期受數字環路濾波器產生的校正信號所控制。本次設計主要采用加、扣脈沖式DCO,該振蕩器的特點是每一個鑒相周期輸出本地估算信號是超前或者滯后于輸入信號的信息,經濾波器處理后輸出加或扣脈沖信號,以此控制DCO的輸出相位。

DCO根據DLF輸出的Insert和Deduct來調節本地時鐘,輸出與曼徹斯特碼位信號同相同頻的時鐘。另外,DPD和DLF的工作時鐘也由DCO產生(Clk_DPD和Clk_DLF同相,前者是后者頻率的1/2),構成了DPLL系統閉環。DCO原理圖如圖5所示。一般DCO分為三個工作模塊,即高速振蕩器、相位調節器和分頻器。由于本次設計的特殊性,將DCO劃分為兩個工作模塊,即將相位調節器和分頻器合并,由DLF產生的Insert和Deduct來指導相位調節,并輸出系統要求的位信號時鐘。

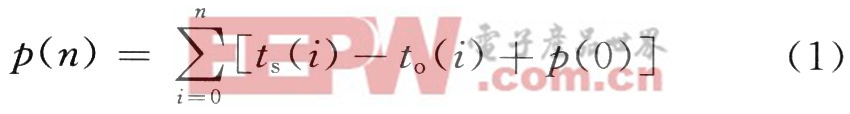

相位調節與分頻輸出如圖6所示。

由于之前的DLF的Mod為8,而Clk_DLF的頻率是500 kHz,周期即2μs,所以每次調節的相位最小單位為120 ns,20 ns×(5+1)=120ns。DLF在同一方向上接到DPD的Sign信號4次后動作,由于本次項目做曼徹斯特解碼時,前導碼是32個,換算成位信號有64個,由于曼徹斯特碼是10交替的,故輸入信號的有效跳變是32次。經過多次仿真和實驗,DPLL一般在前25個前導碼內即可穩定,穩定后在120 ns的范圍內跳動。

3 鎖相環路建模及分析

定義如下變量:ts為外加信號周期;to為反饋信號周期;p(n)為輸出信號和外加信號的相位差。當輸出信號和外加信號的相位差小于π時,鑒相特性是線性的,如圖7所示。

|

|

數字通信相關文章:數字通信原理

鑒相器相關文章:鑒相器原理

評論