基于FPGA的無線同播頻率校準裝置的設計

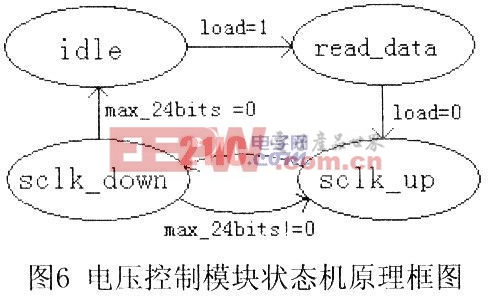

電壓控制模塊的狀態(tài)機如圖6所示,其工作方式是:

(1)idle狀態(tài)時,ready輸出賦為1,sclk賦為1,sync賦為1,max_24bits賦為24。

(2)當load=1時,狀態(tài)轉(zhuǎn)至idle,sync賦為0,data reg通過level和step引腳的值產(chǎn)生相應的控制幀。

(3)當load=0時,狀態(tài)轉(zhuǎn)至sclk_up,sclk賦為1,din賦為data_reg[max_24bits-1]。

(4)狀態(tài)轉(zhuǎn)至sclk down,sclk賦為0,max_24bits自減1。當max_24bits=0時,狀態(tài)轉(zhuǎn)至idle;否則狀態(tài)轉(zhuǎn)至sclk_up。

狀態(tài)sclk_up和sclk_down的循環(huán)是用于產(chǎn)生控制DAC8552的時鐘和數(shù)據(jù),din通過max_24bits這個寄存器實現(xiàn)對data_reg從高到低逐位輸出。

3 實驗結(jié)果

3.1 軟件仿真

利用Libero 8.0開發(fā)環(huán)境集成的Modelsim軟件對電壓控制模塊設計進行仿真。模擬寫入DAC8552的A、B通道數(shù)據(jù)為1010 1111 OO10 1011,十進制為44843,折算為電壓值是2.258V。仿真時序圖如圖7所示,滿足DAC8552接口的時序要求。

3.2 板上調(diào)試

將程序燒入FPGA運行,并通過頻率計實際測量,測量結(jié)果如圖8所示。由于頻率計的精度只達到1Hz,測量的數(shù)據(jù)會有所偏差。考慮到校準后的頻偏已經(jīng)接近+0.05ppm(+0.64Hz),證明系統(tǒng)功能已經(jīng)實現(xiàn)。但系統(tǒng)的效率不夠高,需時過長,算法有待改善。

4 結(jié)束語

本設計通過FPGA、高精度DAC、壓控恒溫晶振和GPS信號接收模塊,成功實現(xiàn)了同播系統(tǒng)發(fā)射設備的頻率校準。除了同播系統(tǒng),本設計還可應用于衛(wèi)星信號同步、跳頻通信的相關(guān)領(lǐng)域,發(fā)展空間十分廣闊。

評論