基于FPGA的無線同播頻率校準裝置的設計

1.3 分級控制方案

基于效率和精度的需要,本設計采用分級控制方案。GPS秒脈沖信號的精度誤差為20ns,折算12.8MHz頻率,最大頻偏為20ppm。若以1秒作為時長比較脈沖數,調整的精度無法達到要求,同頻干擾依然存在。由于秒脈沖信號的精度誤差呈均勻分布,加長檢測的時間可以提高信號精度,從而提高校準精度。但校準效率會下降,發射準備時間增加。另一方面,DAC的控制方式也影響系統的精度和效率。單次調整幅度大,效率高但精度低,幅度小則需時過長,所以不能以固定的幅度調整。根據VC-TCXO和DAC8552的參數,DAC最小的調整幅度為0.015Hz,DAC數值與VC-TCXO頻率的關系是:

f(b)=12.8MHz+(b-b)×O.015Hz

式中f(b)是當前VC-TCXO頻率,b是FPGA寫入DAC的數值,b’是VC-TCXO輸出12.8MHz時對應的DAC數值。VC-TCXO的電壓可調范圍是1.65±1.0V,折算b的有效范圍為12 909~52 627。

為了平衡精度和效率的需要,系統采用了分級控制的方案。如表1所示,系統控制的邏輯分為五級。等級3的頻偏和調整幅度最小,檢測時間最長。脈沖數上下限用于固定時長內脈沖數的比較,判斷是否需要調級。VC-TCXO的溫度和老化的因素使晶體頻率的上下限改變,所以等級1沒有計數脈沖下限,等級5沒有上限。FPGA根據當前的級別設定檢測時間,再通過收到的脈沖數判斷升級、降級或是調整電壓值。本文引用地址:http://www.czjhyjcfj.com/article/191781.htm

2 FPGA設計

2.1 FPGA頂層設計

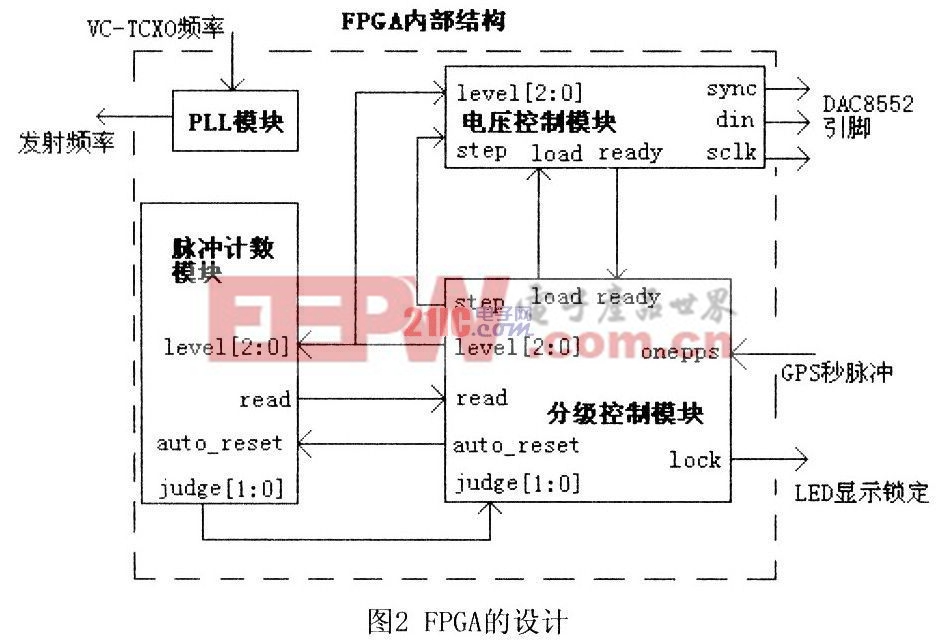

FPGA的設計采用自頂向下的設計方法,用Verilog HDL語言描述,在Actel公司的開發軟件libero8.0中進行綜合、優化、仿真和定時分析。頂層設計由PLL、分級控制、脈沖計數模塊以及電壓控制模塊組成,如圖2所示。

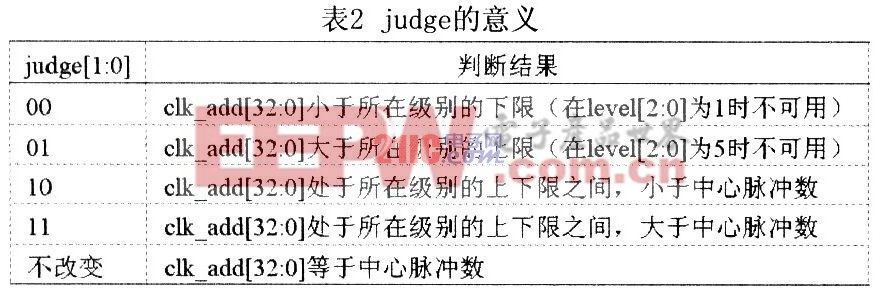

工作過程為:首先,初始化FPGA,電壓控制模塊將DAC8552的電壓輸出值置于中位(1.65V),分級控制模塊的開始分級設定為3,并通過level[2∶0]連線將級別賦給脈沖計數模塊和電壓控制模塊;分級控制模塊收到GPS秒脈沖時,通過auto reset啟動脈沖計數模塊,收到read信號時讀入judge[1∶0],judge[1∶0]的意義如表2所示。如果judge[1∶0]=00,level[2∶0]不為1,level[2∶0]降級;judge[1∶0]=01,level[2∶0]不為5,level[2∶0]升級;judge[1∶0]為10或11,通過step和load引腳調整電壓控制模塊。

評論