基于FPGA快速A 律壓縮編碼的設(shè)計與實現(xiàn)

摘要:本文針對A律13折線法的算法特點,提出一種并行數(shù)據(jù)處理算法,實現(xiàn)了編碼的流水線操作。運用VHDL語言將其在FPGA中實現(xiàn),借助quartus II6.0平臺進行驗證,并對驗證結(jié)果進行分析,評估了系統(tǒng)的性能,證實了該算法的優(yōu)越性和高效性。

關(guān)鍵詞:A律壓縮編碼,FPGA,VHDL

1引言

在信號處理過程中,我們通常將模擬信號轉(zhuǎn)化為數(shù)字信號進行處理或傳輸。原始數(shù)據(jù)用取樣的方法進行采集,通過A/D轉(zhuǎn)換將模擬信號變成數(shù)字信號。但是這樣的數(shù)字信號由于碼位多,在傳輸過程中占用帶寬多,傳輸率也低。為了提高傳輸效率,必須對原始數(shù)據(jù)進行量化處理。在實際運用中通常采用非均勻量化。采用輸入信號幅度和量化輸出數(shù)據(jù)之間定義了兩種對應關(guān)系,一種是在北美日本使用的 律;另一種是在歐洲中國大陸使用的A律。A律壓縮重要運用于數(shù)字電話通訊中的語音壓縮編碼,如何實現(xiàn)快速壓縮已成為實際應用的關(guān)鍵。隨著VLSI(超大規(guī)模集成電路)特別是FPGA技術(shù)的日益成熟,基于FPGA的各種壓縮編碼的實現(xiàn)顯示出其獨特的優(yōu)勢和廣泛的應用前景[1-3]。本文針對13折線來的算法特點,提出一種并行數(shù)據(jù)處理且適合于實現(xiàn)編碼流水線作業(yè)的改進算法,運用VHDL語言將其在FPGA中實現(xiàn),借助Quartus II 6.0平臺對其進行驗證、仿真,并對仿真結(jié)果進行分析,評估了系統(tǒng)的性能,證實了該算法的優(yōu)越性和高效性。

2 原理

所謂A壓縮律也就是壓縮律具有如下特性的壓縮律[4]:

:

:

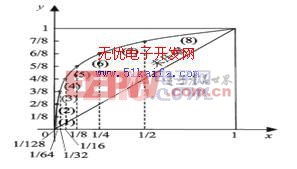

式中x ―歸一化的壓縮器輸入電壓; y―歸一化的壓縮器輸出電壓; ―壓擴參數(shù),表示壓縮程度。實際中, 壓縮律通常采用13折線(圖1)來近似。

圖1 13折線示意圖

評論