采用MAX II器件實現FPGA設計安全解決方案

基于SRAM的FPGA是易失器件,需要外部存儲器來存儲上電時發送給它們的配置數據。在傳送期間,配置比特流可能會被捕獲,用于配置其他FPGA。這種知識產權盜竊損害了設計人員的利益。

本文引用地址:http://www.czjhyjcfj.com/article/191381.htm本文提供的解決方案可防止FPGA設計被拷貝,即使配置比特流被捕獲,也可以保證FPGA設計的安全性。通過在握手令牌由MAX II器件傳送給FPGA之前,禁止用戶設計功能來實現這種安全性。選用MAX II器件來產生握手令牌,這是因為該器件具有非易失性,關電時可保持配置數據。而且,對于這種應用,MAX II器件是最具成本效益的CPLD。本文還介紹了采用這種方案的一個參考設計。

硬件實現

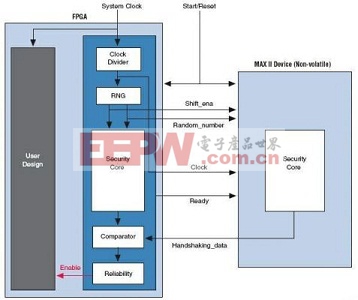

FPGA設計安全解決方案的硬件實現如圖1所示。MAX II器件產生連續的握手令牌,發送至FPGA,以使能用戶設計。FPGA和MAX II器件之間傳送5個信號:clock、shift_ena、random_number、ready和handshaking_data。

圖1:FPGA設計安全方案的硬件實現。

一旦FPGA經過配置后,它向MAX II器件提供連續時鐘。同時連接至FPGA和MAX II器件的啟動/復位信號必須置位,以啟動系統工作。FPGA中的隨機數發生器(RNG)開始為FPGA和MAX II器件產生初始計數值(每次上電或者啟動/復位信號置位時,僅向MAX II器件發送一次隨機數)。隨機數準備好后,shift_ena信號變為高電平,采用random_number信號,隨機數串行移位至MAX II器件。隨機數全部移位至MAX II器件后,ready信號置位,指示FPGA可以接收來自MAX II器件的握手令牌。

配置之后,由于Enable信號還是邏輯低電平,FPGA中的用戶設計功能被禁止。只有MAX II器件送出的握手令牌和FPGA內部產生的數據相匹配,Enable信號才會置位,啟動用戶設計功能。這兩個數據之間出現差異時,Enable信號變為低電平,禁止用戶設計功能。MAX II器件中產生握手令牌和FPGA器件中產生數據的方法和過程相同。如果沒有正確的令牌,FPGA器件中的用戶設計功能被禁用。這樣,即使配置比特流被捕獲,也可以防止用戶設計被拷貝。

設計構建模塊

FPGA的設計安全組成包括一個時鐘分頻器、隨機數發生器(RNG)、安全內核、比較器和可靠性部分,而MAX II器件的設計安全組成只包括圖1所示的安全內核。

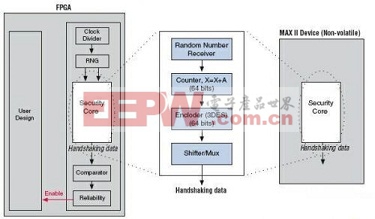

FPGA和MAX II器件使用的安全內核相同,如圖2所示,由以下部分構成:隨機數接收器、64位計數器、編碼器、移位器/復用器。

圖2:FPGA和MAX II器件的安全內核。

分頻器相關文章:分頻器原理

評論