基于FPGA的雷達中/視頻數據采集與回放系統設計

3.1.1 數據采集模塊設計

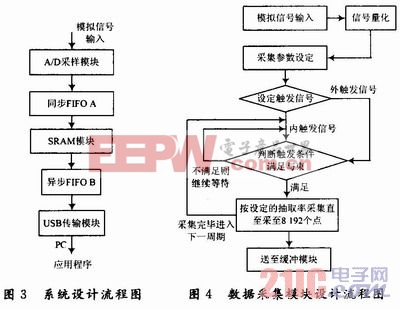

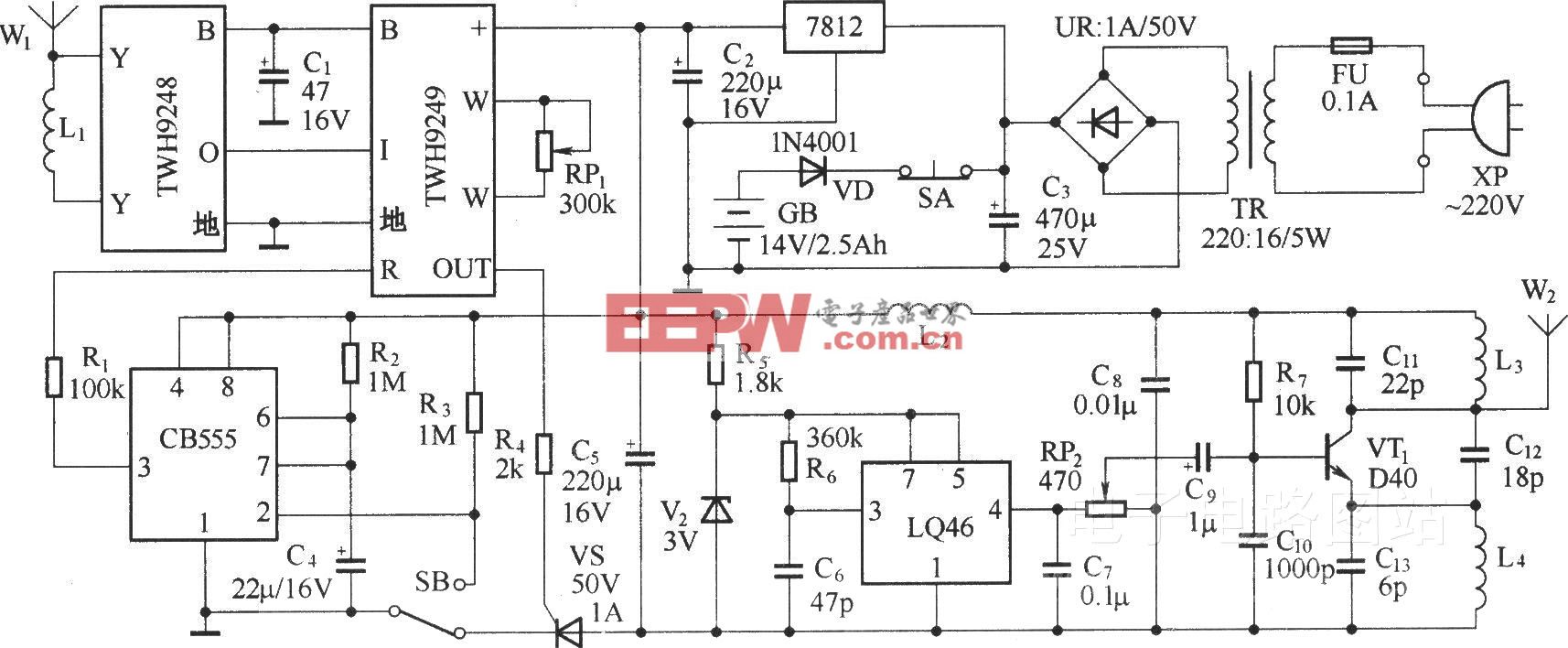

雷達信號采集技術中,采集時序控制與實時數據傳輸是關鍵也是技術的難點所在。為保證采集的連續性,設計中采用了FPGA內部雙FIFO的緩沖技術、外置專用緩沖芯片技術與計算機公用緩沖區環行存儲技術。該模塊的詳細軟件設計流程如圖4所示。

3.1.2 數據緩沖模塊設計

數據緩沖模塊設計了同步FIFO A和異步FIFO B。其中FIFO A的一端接收A/D轉換數據,另一端將數據傳輸給外部SRAM;FIFO B的一端接收SRAM的數據,另一端將數據傳輸給USB單片機的FIFO。

3.1.3 測頻模塊設計

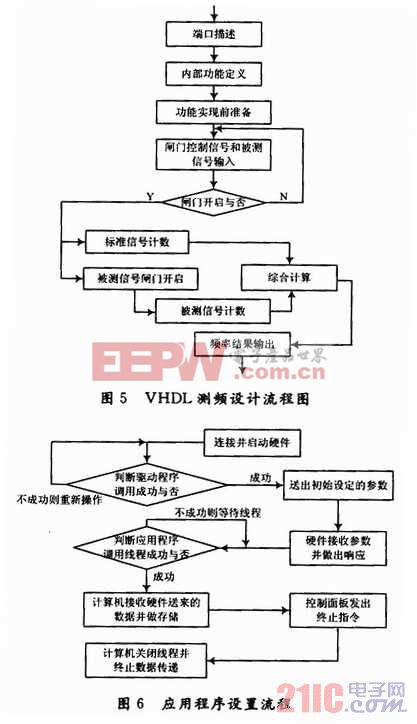

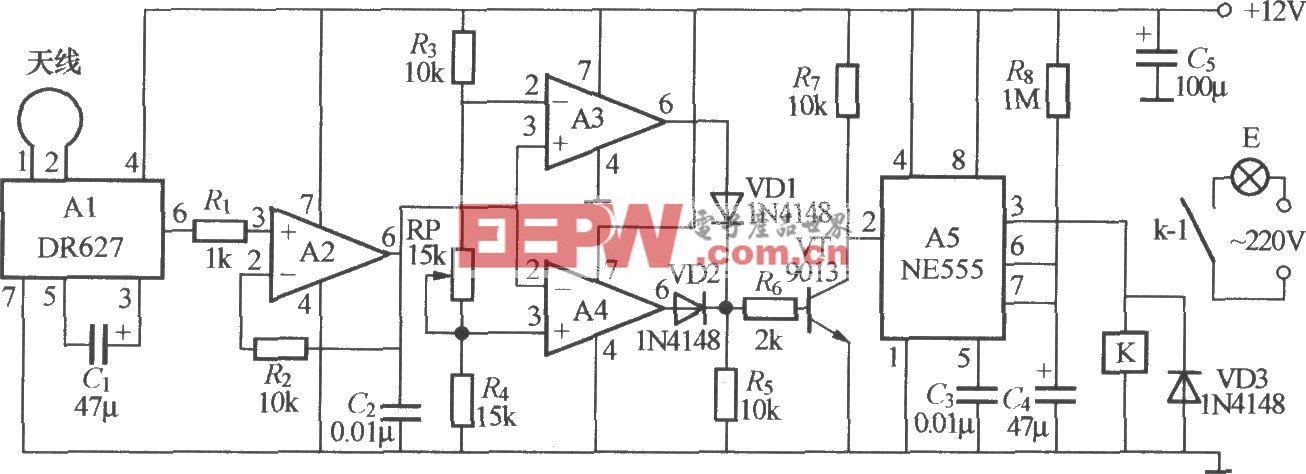

基于傳統測頻原理的頻率計的測量精度將隨被測信號頻率的下降而降低,在實用中有較大的局限性,而等精度頻率計不但具有較高的測量精度,而且在整個頻率區域能保持恒定的測量精度。綜合考慮,本系統采用等精度頻率計的測量方法。其基本流程圖如圖5所示。

3.1.4 測電壓模塊設計

采集信號經A/D變換器量化編碼以后,可以根據量化得到的結果進行信號幅度值的計算。同時考慮到采集到的信號尤其是正弦波、三角波等信號在測量時會發生抖動,所以在進行電壓測量時,采用了取平均值和對信號進行平滑處理相結合的方法提高測電壓的精度,設計實現對信號峰峰值、平均值的測量。

評論