基于FPGA的高階音頻均衡濾波器設計

摘要:文中設計的均衡濾波器充分利用FPGA內部資源、時間換取空間的方法,在EP1C3系列的FPGA內實現1 024階FIR數字均衡濾波器,并通過重載系數,可實現多種頻率響應的均衡特性、簡易數字均衡濾波器的功能,達到了設計目的。

關鍵詞:數字均衡濾波器;FPGA;1 024階;FIR

音頻均衡器作為高品質音響不可或缺的關鍵附屬調節設備,在音效調整修飾方面起著至關重要的作用。一般音頻均衡器有數字和模擬兩種實現方法,模擬方法用有源和無源濾波器組實現,受器件溫度等特性的影響,難以達到較高的可靠性和一致性,且成本較高。數字實現方法采用數字濾波器,具有較高的靈活性和可靠性。常用的數字濾波器有IIR和FIR兩種。IIR濾波器結構簡單,所需的存儲空間小,但其相位是非線性;FIR濾波器是線性相位濾波器,這對高品質音效處理是必要的。本文通過在FPGA內設計了1 024階FIR濾波器實現數字均衡濾波,通過系數的重載實現多種頻率響應的均衡特性。

1 總體概述

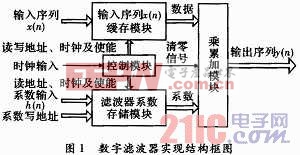

文中設計的FIR音頻均衡濾波器采用多相濾波結構,用時間換取空間,節省FPGA內部資源,以達到在固定資源下的最大階數。實現結構框圖如圖1所示。

輸入序列以及濾波系數分別存儲在緩存陣列中,在時鐘同步下由控制模塊通過生成相應的讀寫地址及使能信號,使其按照一定次序輸出到乘累加模塊進行運算,并輸出最終結果。系數可通過外部輸入重載,以實現不同的均衡特性。EP1C3系列FPGA共有13個M4K塊,每個為256 ×18位,取數據和系數的位寬為16位。為了充分利用有限資源,并考慮處理速度及音頻信號速率要求,取每個緩存子模塊的存儲深度為256,即將乘累加模塊復用256次,每256個系統時鐘周期運算一個采樣點數據,輸出一個濾波結果。每個緩存子模塊占用一個M4K塊,連續4個子模塊串聯,就可實現256 x4=1 024階的要求,再考慮系數占用的空間,總共消耗8個M4K塊。這也是在有限資源下能實現的最高階數。

2 各模塊實現

2.1 輸入序列緩存模塊

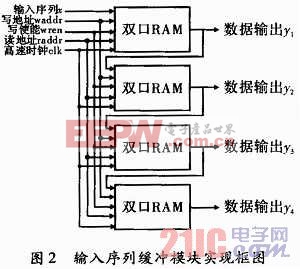

輸入序列緩沖模塊采用雙口RAM模塊實現,將4個級聯使用,如圖2所示。4個子塊使用相同的讀寫地址及使能信號,采樣數據從第一個子塊輸入,第一個子塊的數據輸出端與下一級子塊的輸入端直接相連,依次類推。每個緩存子塊的數據y1~y4都輸出給乘累加模塊進行運算。

該模塊的關鍵是讀寫地址的控制,寫地址waddr必須滯后讀地址raddr一個時鐘周期,這樣子塊當前輸出數據會在下個時鐘寫入下一個子塊的相應單元。256個周期后,子塊的數據整體移到下一個子塊。

評論