線性調頻信號基于FPGA IP核的脈沖壓縮設計

摘要:為實現線性調頻信號的數字脈沖壓縮,設計一個FPGA硬件平臺,并著重提出一種基于FPGA IP核的脈沖壓縮設計方法。針對脈沖壓縮進行了理論分析和Matlab仿真,設計完成后對系統軟、硬件進行了全面測試,并根據實測數據對脈沖壓縮結果進行了分析。結果表明,該系統可實現1 024點的脈沖壓縮功能,主副瓣比、主瓣寬度等指標與理論仿真結果一致。該方法的參數設置靈活,可以簡化軟件設計,縮短研發周期。

關鍵詞:FPGA;IP核;脈沖壓縮;Matlab

0 引言

根據雷達分辨理論,為了使雷達作用距離遠,同時又具有高的測距精度和好的距離、速度分辨力,雷達發射信號必須是大帶寬長脈沖形式。脈沖壓縮過程就是對大時寬帶寬積信號在接收時進行匹配濾波,重新調整信號中各頻率分量的相對相位以得到窄脈沖信號,從而提高雷達的距離分辨力和測距精度。由于線性調頻信號產生較為方便,而且它對多普勒頻率不敏感,因此實際工程中常采用線性調頻信號作為脈壓信號。

近年來,隨著現場可編程門陣列(FPGA)在雷達信號處理中的廣泛應用以及FPGA芯片技術的發展,為大家提供了一種較好解決數字脈壓的途徑。其中,利用IP核設計FPGA數字系統成為一種趨勢,這些知識產權核可以大大簡化FPGA的設計,加快設計速度,縮短研發周期,而且經過不斷的優化,IP核具有了更好的精度和更快的運算速度,實際的工程應用效果很好。

本文以此為出發點,對線性調頻信號的脈沖壓縮進行了研究,仿真,并提出了一種采用IP核設計脈沖壓縮的方法。

1 線性調頻信號的脈沖壓縮

1.1 脈沖壓縮的實現原理

脈沖壓縮可以采用“共軛濾波器對”的匹配濾波法和相關處理法。匹配濾波法對應于頻域相乘,相關處理法對應于時域卷積。依據傅里葉變換理論:時域卷積等效于頻域乘積。因此這兩種方法是等效的,只是一種方法在頻域實現,而另一種方法在時域實現。考慮到運算量,工程上一般采用頻域法,可以利用快速FFT算法提高計算速度,然后將雷達回波與匹配濾波系數的頻域響應相乘,再經過IFFT處理得到脈沖壓縮結果。匹配濾波系數只與發射信號有關,預先可知,一般預先算好。

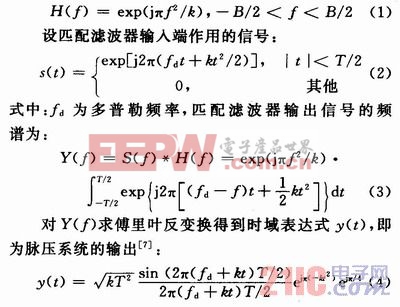

1.2 線性調頻信號的脈沖壓縮

一般在時寬帶寬積BT>30時,可以近似認為線性調頻信號具有矩形振幅頻譜,因此其匹配濾波器也應該具有矩形帶通振幅特性。線性調頻信號的匹配濾波器的近似頻率特性可描述為:

可以看出,線性調頻的脈沖壓縮結果具有sine函數形狀。主瓣寬度為1/B,第一旁瓣電平約為-13.2 dB。如果是多目標環境,較大的旁瓣會埋沒附近的小目標信號,為了抑制旁瓣,可以采用加權技術。其實質就是對信號進行失配處理以抑制旁瓣,其副作用是使輸出信號的主瓣降低并展寬。

1.3 理論仿真

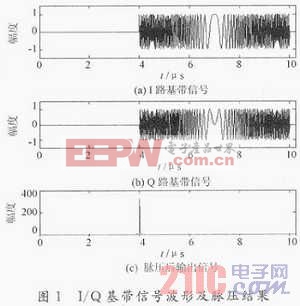

設匹配濾波器的輸入信號是線性調頻I/Q基帶信號,帶寬為40 MHz,采樣頻率為100 MHz,脈沖寬度為6μs,信號幅度為1,通過Matlab對其進行脈沖壓縮仿真。圖1中是輸入的I/Q基帶信號波形以及脈壓后的結果。從圖中可以看到脈壓后產生的窄脈沖,波形具有sine函數性質,除主瓣外,時間軸上還有延伸的一串副瓣;還可看出,經過海明加權后,第一副瓣比主瓣下降約40 dB,但主瓣寬度也有相應的展寬。如圖2所示。

評論