基于FPGA控制VGA顯示的多通道數字示波器的設計

摘要:為了實現對0~1 MHz的信號進行測量以及顯示的目的,制作了基于SOPC技術的VGA顯示數字存儲示波器。采用硬件與軟件相配合的設計方法,主要模塊有基于FPGA的最小系統模塊、信號調理電路模塊、AD采樣模塊、觸發電路模塊、VGA顯示模塊、4×4矩陣鍵盤模塊和RAM存儲以及FLASH存儲模塊。具有模擬信號可進行任意電平觸發、數字信號可使用上升沿和下降沿觸發、存儲回放、垂直靈敏度檔位設置、掃描速度檔位設置、VGA顯示多個界面等特點。通過波形測量實驗,得到較好的顯示波形。

關鍵詞:FPGA;數字示波器;A/D采樣;VGA顯示

隨著信息技術的發展,對信號的測量技術要求越來越高,示波器的使用越來越廣泛。模擬示波器使用前需要進行校正,使用比較麻煩;而數字示波器,由于受核心控制芯片的影響,對輸入信號的頻率有嚴格的限制。基于FPGA的數字示波器,其核心芯片可達到50萬門,配合高速外圍電路,可以測量頻率為1 MHz的信號,有效地克服了以往示波器的不足。

1 系統方案設計

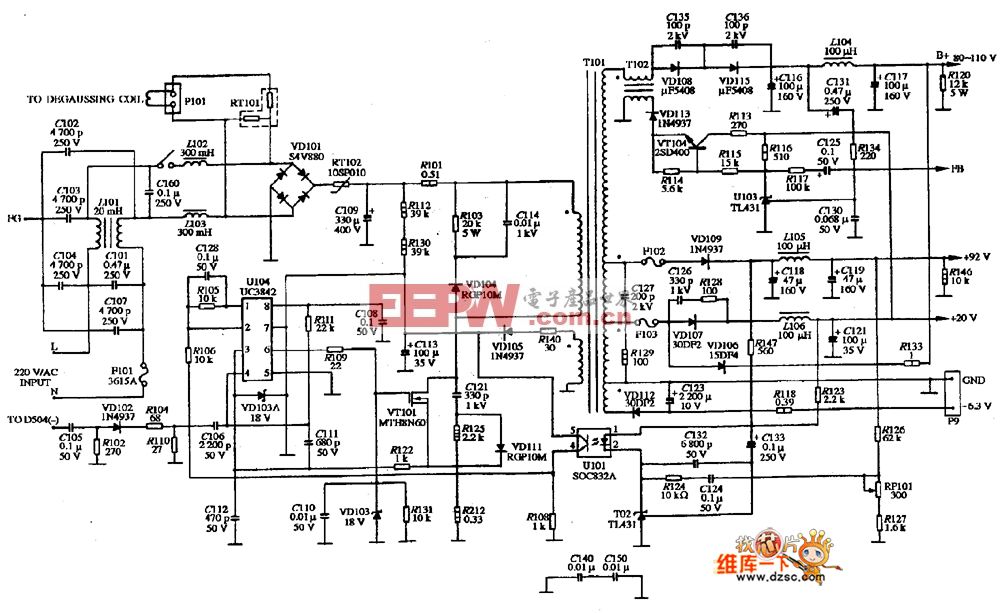

設計的數字示波器系統主要使用了Xilinx系統的開發環境,并在此環境內部建立了AD采樣控制模塊、鍵盤控制模塊、VGA顯示模塊等多個模塊,從很大程度上減少了硬件電路的搭建,也因此提高了系統的穩定性和可靠性,系統框圖如圖1所示。

另外,設計使用XPS將32位的MicroBlaze微處理器嵌入到了FPGA中,實現了可編程片的嵌入以及在可編程片上的系統設計。MieroBlaze通過LBM總線訪問片上的存儲模塊BlockRAM,然后通過OPB總線上掛接外設進行接口連接和驅動。

VGA顯示部分采用雙緩沖機制進行工作,在FPGA內部建立RAM,按照一定時序降RAM內的緩存數據映射到VGA顯示屏上。

2 硬件設計

2.1 信號調理電路模塊

信號調理電路模塊,對輸入的模擬信號進行處理,由于輸入電壓幅度為-2.5~+2.5 V之間,而后一級的AD模塊采用了12位的高速A/D轉換芯片ADS804,只能對0~2 V的電壓進行模/數轉換,故需要將輸入電壓先抬升為0~5 V,在應用運算放大器進行比例縮小,達到0~2 V的模數轉換要求。

評論