ModelSim和QuestaSim功能簡介及仿真介紹

ModelSim是工業界最優秀的語言仿真器,它提供最友好的調試環境,是作FPGA、ASIC設計的RTL級和門級電路仿真的首選。它支持PC和UNIX、LINUX平臺,是單一內核支持VHDL和Verilog混合仿真的仿真器。它采用直接優化的編譯技術、Tcl/Tk技術、和單一內核仿真,編譯仿真速度業界最快,編譯的代碼與平臺無關,便于保護IP核,具有個性化的圖形界面和用戶接口,為用戶加快調試提供強有力的手段。全面支持VHDL和Verilog語言的IEEE 標準,以及IEEE VITAL 1076.4-95 標準,支持C語言功能調用, C的模型,基于SWIFT的SmartModel邏輯模型和硬件模型。

本文引用地址:http://www.czjhyjcfj.com/article/190899.htmModelSim支持RTL仿真,門級仿真,時序仿真:

主要特點:

*采用直接編譯結構,編譯仿真速度最快;

*單一內核無縫地進行VHDL和Verilog混合仿真;

*與機器和版本無關,便于數據移植和庫維護;

*與機器無關的編譯代碼編于保護和利用IP;

*簡單易用和豐富的圖形用戶界面,快速全面調試;

*Tcl/Tk用戶可定制仿真器;

*完全支持VHDL/Verilog國際標準,完全支持Verilog 2001;

*支持眾多的ASIC和FPGA廠家庫;

*集成的Performance analyzer幫助分析性能瓶頸,加速仿真;

*靈活的執行模式,Debug模式可以進行高效的調試,效率模式大幅度提高仿真速度。

*加強的代碼覆蓋率功能Code coverage,能報告出statement 、branch、condition、

* expression、toggle、fsm等多種覆蓋率情況,進一步提高了測試的完整性;

*同一波形窗口可以顯示多組波形,并且能進行多種模式的波形比較(Wave Compare);

*先進的Signal Spy功能,可以方便地訪問VHDL 或者 VHDL 和Verilog 混合設計中的下層模塊的信號,便于設計調試;

*支持加密IP;

*集成的 C調試器,支持 用C 語言完成測試平臺和模塊;支持64位的OS;

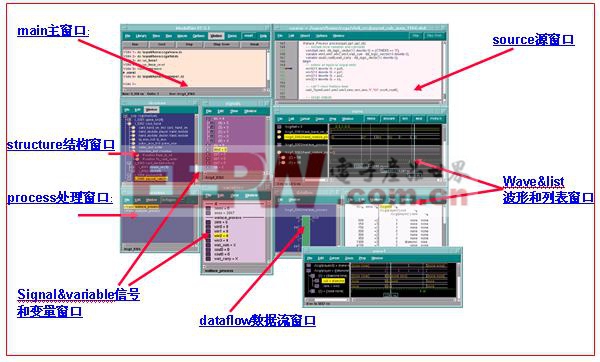

ModelSim用戶界面:

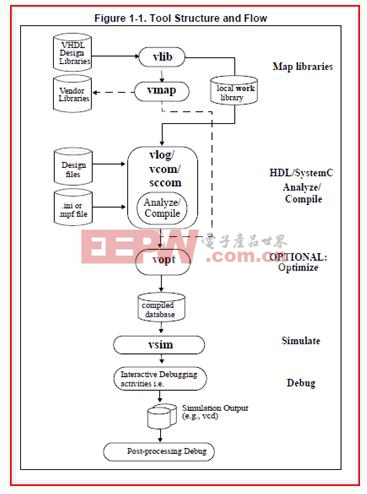

ModelSim設計流程:

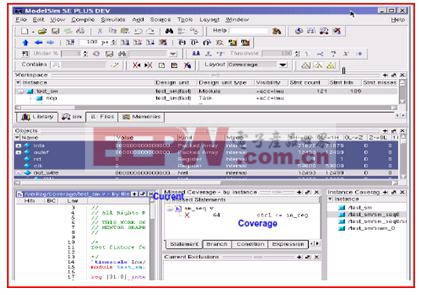

ModelSim coverage驗證:

評論