在低端FPGA中實現LVDS接口設計中的DPA功能

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。ALTERA的高端FPGA,如STRATIX(r) 系列中自帶有DPA電路,但低端的FPGA,如CYCLONE(r)系列中是沒有的。本文主要闡述如何在低端FPGA中實現這個DPA的功能。

本文引用地址:http://www.czjhyjcfj.com/article/190531.htm實現架構

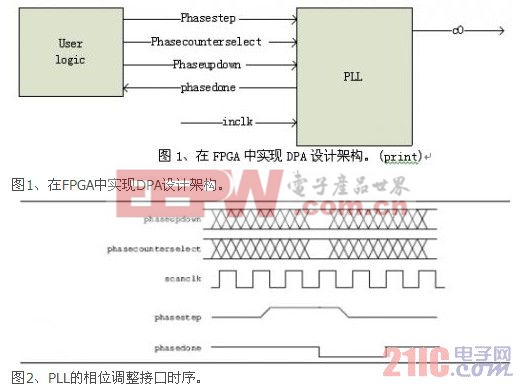

在LVDS輸入接收時,時鐘和數據的相位可能是不確定的,因此我們需要將時鐘的相位作出調整,使得時鐘能穩定的采集到輸入數據。工作的核心就是用鎖相環PLL的相位調整功能,產生若干個時鐘的不同相位,看哪些相位能準確的采集到輸入數據,然后取窗口中間的一個時鐘相位,作為正常工作時的采樣時鐘。比如通過PLL產生0,45,90,135,……,315度8個相移的時鐘,如果0,45,90度相移的時鐘能正確采樣到輸入,那么最后選取中間相位,即45度的時鐘作為采樣時鐘。這樣接口上具有最大的時序裕量,從而保證鏈路的可靠性。圖1為這個設計的基本結構,通過PLL調整相位的接口,產生了時鐘的不同相位來采集數據,最后選擇一個最合適的相位。

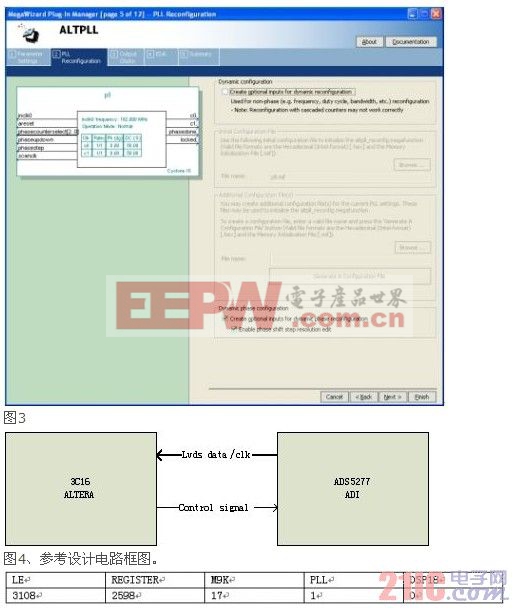

CYCLONE系列的PLL的相位調整接口時序如圖2所示,當用戶邏輯控制phasestep, phasecounterselect與phaseupdown信號時,PLL的輸出時鐘C0就改變一次相位。在QII生成PLL時,用戶必須選上create optional inputs for dynamic phase reconfigure,否則缺省是不會有這些管腳的,如圖3所示。另外必須在output clock tab中寫入phase shift step resolution的值,這樣才能確定每次相位調整的步長。

應用實例

本例中的參考設計采用CYCLONE3器件,與ADI公司的ADS5277接口,已經在硬件上測試過,證明是有效的。ADS5277是一款8通道高速ADC芯片,主要用于超聲設備以及測試設備中。圖4是該參考設計電路框圖。

ADS5277送到FPGA的是一個192MHz的時鐘,8路LVDS數據,速率是384Mbps。上電復位后ADS5277發送的數據是‘0101010101……’,FPGA啟動DPA電路,準確確定時鐘相位后再通過控制信號,使得ADS5277發送‘000000111111……’這樣的PATTERN,FPGA可以確定字的邊界,這一步成功以后,FPGA就可以通過控制信號讓ADS5277發送正常工作時的數據,因為經過了時鐘相位調整這一過程,以后的數據采樣是非常穩定的,不會受到溫度電壓變化來的影響。

當然這個設計可以和所有LVDS發送芯片接口,并不只限于ADS5277。甚至可以應用于ALTERA高端FPGA中,比如STRATIX4的帶有DPA專用電路的管腳只分布在左右BANK,而用到這個設計的話,上下BANK的IO也能使用。DPA設計所消耗的邏輯資源是非常小的,選用器件為3C16F256C8, 如表1所示。

評論