3D芯片堆疊技術(shù)現(xiàn)狀

盡管最近幾年以TSV穿硅互聯(lián)為代表的3D芯片技術(shù)在各媒體上的出鏡率極高,但許多人都懷疑這種技術(shù)到底有沒有可能付諸實用,而且這項技術(shù)的實際發(fā)展速度也相對緩慢,目前很大程度上仍停留在“紙上談兵”的階段。不過,許多芯片制造商仍在竭力推進基于TSV的3D芯片技術(shù)的發(fā)展并為其投入研發(fā)資金,這些廠商包括IBM,Intel,三星,東芝等等,3D芯片技術(shù)的優(yōu)勢在于可以在不需要改變現(xiàn)有產(chǎn)品制程的基礎(chǔ)上增加產(chǎn)品的集成度,從而提高單位芯片面積內(nèi)的晶體管數(shù)量。

本文引用地址:http://www.czjhyjcfj.com/article/190447.htm在最近舉辦的GSA存儲大會上,芯片制造業(yè)的四大聯(lián)盟組織-IMEC, ITRI, Sematech以及SEMI都展示了他們各自在基于TSV的3D芯片技術(shù)方面的最新進展。

SEMI聯(lián)盟組織旗下的一個3D芯片技術(shù)工作組本周召開了第一次聯(lián)合會議,會上他們草擬出了一套TSV技術(shù)用晶圓坯以及制造用設(shè)備的標(biāo)準(zhǔn)。SEMI聯(lián)盟組織旗下共有三個與3D芯片技術(shù)有關(guān)的工作組,而且他們目前還在組織第四個與之有關(guān)的工作組,這個新成立的工作組將由芯片生產(chǎn)用設(shè)備制造行業(yè)的老大應(yīng)用材料公司領(lǐng)銜。

而另外一個工業(yè)聯(lián)盟組織Sematech也在積極拓展自己的3D芯片研發(fā)計劃。令人稍感意外的是,Analog Devices最近也宣布加入了由Sematech組織的“3D芯片設(shè)計啟動中心”組織,目前該組織的成員有Altera, LSI, 安森美半導(dǎo)體以及高通等幾家。

3D堆疊技術(shù)的誘因:

另外一些組織和公司也都在積極開發(fā)基于TSV的3D芯片技術(shù)。究其原因,是因為許多芯片廠商都擔(dān)心將來繼續(xù)縮減制程尺寸時,所花費的成本將難以承受,甚至不久的將來可能會被迫停止芯片制程縮減方面的研發(fā)。

所有這些行動表明,除了向二維方向縮減制程尺寸之外,業(yè)界也在積極考慮向三維TSV芯片堆疊方向發(fā)展的方案。多年以來,芯片制造商一直在談?wù)摶赥SV的3D芯片堆疊技術(shù),不過除了在CMOS圖像傳感器領(lǐng)域有推出過采用類似技術(shù)的產(chǎn)品之外,這項技術(shù)還遠遠沒有進入主流范疇,導(dǎo)致這種現(xiàn)象的原因則是研發(fā)成本高,缺乏標(biāo)準(zhǔn)等因素。

2.5D與3D芯片堆疊技術(shù):

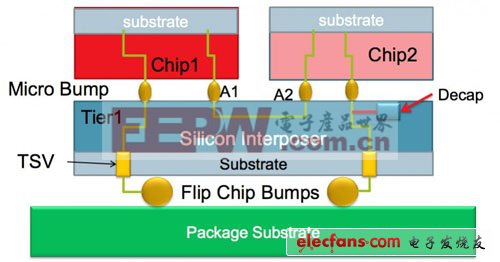

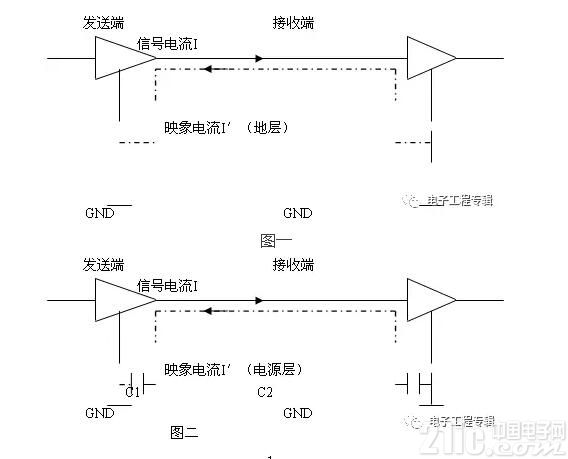

2.5D芯片堆疊結(jié)構(gòu)

理論上說,3D芯片堆疊技術(shù)的實現(xiàn)可分兩步走,第一階段是先采用借助硅中間互連層的2.5D技術(shù),這種技術(shù)中雖然也有使用TSV技術(shù),但如上圖所示,功能芯片(chip1/2)中并沒有制出TSV結(jié)構(gòu),而是把TSV結(jié)構(gòu)設(shè)置在專門的襯底中,功能芯片通過microbump與中間互連層(interposer)連接,再通過一層TSV襯底連接到3D芯片封裝用襯底上;而第二階段則會將TSV結(jié)構(gòu)直接植入功能芯片之中。

而現(xiàn)在,多家組織已經(jīng)組建了許多新的,面向主流應(yīng)用的3D芯片堆疊項目組。舉例而言,Semtech組織便正在與IBM公司進行這方面的合作,這個項目的目標(biāo)是將模數(shù)轉(zhuǎn)換器芯片與DSP芯片利用TSV 3D堆疊技術(shù)連接在一起,這兩種芯片將通過一層中間互聯(lián)層(interposer)連接在一起,該互連層的峰值帶寬可超過1.3Tbps.

3DIC技術(shù)在內(nèi)存領(lǐng)域的應(yīng)用熱點:Wide I/O

另外,以Hynix,三星等為首的組織則在積極推廣可將TSV 3D堆疊技術(shù)帶入主流應(yīng)用領(lǐng)域的另外一項計劃,即Wide I/O內(nèi)存接口技術(shù),這項技術(shù)面向手機,平板電腦等相關(guān)產(chǎn)品。

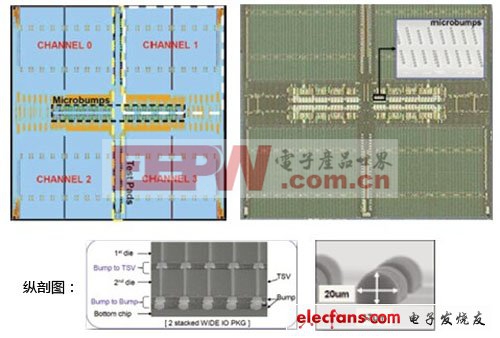

三星的Wide I/O內(nèi)存芯片內(nèi)部結(jié)構(gòu)

JEDEC組織目前還在審核Wide I/O內(nèi)存接口技術(shù)標(biāo)準(zhǔn),這種內(nèi)存接口的位寬達512bit,可以增大內(nèi)存芯片與邏輯芯片之間的數(shù)據(jù)傳輸帶寬,其峰值傳輸率可達12.8GB/s,帶寬要比常規(guī)的LP DDR2接口高出了3倍之多。

LPDDR2是目前移動設(shè)備用內(nèi)存的主流接口標(biāo)準(zhǔn)。而Wide I/O則是三星等廠商計劃用于取代LPDDR2的接口標(biāo)準(zhǔn),Wide I/O計劃將分兩個階段實現(xiàn),第一階段的Wide I/O將實現(xiàn)將4塊內(nèi)存芯片通過TSV技術(shù)實現(xiàn)互聯(lián),組建高位寬4通道芯片,然后再利用TSV技術(shù)將這種高位寬4通道芯片堆疊在一起。高位寬4通道芯片內(nèi)部的四塊芯片采用微凸焊(microbump或稱μ-bump)互聯(lián)的方法實現(xiàn)相互連接。據(jù)預(yù)測,采用這種技術(shù)的產(chǎn)品有望在2014/2015年間出現(xiàn),不過也有人認(rèn)為這項技術(shù)實用化可能需要更多的時間。

Rambus公司高級副總裁兼半導(dǎo)體業(yè)務(wù)部門的總經(jīng)理Sharon Holt則認(rèn)為,由于這項技術(shù)十分復(fù)雜加上高額的研發(fā)成本,因此基于TSV的Wide I/O接口技術(shù)可能要再過“5-10年”才有望實用化。同時他還認(rèn)為業(yè)界不太可能直接從現(xiàn)有的LPDDR2標(biāo)準(zhǔn)轉(zhuǎn)換到Wide I/O標(biāo)準(zhǔn),因為從時間上看,LPDDR2技術(shù)去年便已經(jīng)有實際的產(chǎn)品問世,而Wide I/O技術(shù)現(xiàn)在看則仍是八字還沒一撇。

這樣,LPDDR2和Wide I/O之間便會出現(xiàn)一個空檔期。而Rambus則正好可以見縫插針地推廣其移動內(nèi)存用XDR接口標(biāo)準(zhǔn)。

在這次GSA大會上,Holt還表示移動用內(nèi)存標(biāo)準(zhǔn)與PC用內(nèi)存標(biāo)準(zhǔn)終將實現(xiàn)一統(tǒng),也就是說目前移動設(shè)備上使用的LPDDR2技術(shù)有可能被PC內(nèi)存用上,他并稱其為“統(tǒng)一內(nèi)存系統(tǒng)”。

不過其它廠商則看法不同。比如三星公司的高管Jim Elliott雖然同意“統(tǒng)一內(nèi)存系統(tǒng)”的提法,但他認(rèn)為促成內(nèi)存標(biāo)準(zhǔn)一統(tǒng)的技術(shù)將是基于TSV的Wide I/O技術(shù)。

評論