基于FPGA的LCD測試用信號發生器設計

摘要:在檢測液晶屏特性和質量時,需要控制液晶屏顯示一些標準信號。已有的一些信號產生設備產生的是AV信號、VGA信號或YPhPr信號等模擬制式的信號。模擬制式的信號需要經過圖形處理器(GPU)轉換成數字LVDS信號,然后輸入到液晶屏的掃描控制電路產生相應圖像。這個過程不可避免的會使圖像信號產生一定程度的失真與損耗,影響圖像質量。旨在設計一種新型信號發生器,該發生器產生的數字圖像信號轉換成數字LVDS信號后,直接輸入液晶屏,以避免信號傳輸過程產生的失真與損耗。

關鍵詞:液晶顯示;信號發生器;FPGA;LVDS

0 引言

液晶顯示已成為目前平板電視與計算機顯示終端的主流,液晶顯示器的研究設計、生產、檢驗等部門甚至消費者需要用一些定量或定性的方法和指標去檢驗液晶顯示器的質量和特性。

液晶電視與液晶顯示器是數字化的顯示終端,為了與目前的計算機主機顯卡相兼容,計算機顯示器普遍保留了模擬制式的VGA接口,作為家用的液晶電視也普遍預留了VGA接口用來接收模擬的VGA顯示信號。目前的一些LCD白平衡調整及檢測設備所用的信號發生器都采用了從液晶電視和顯示器的AV信號接口、VGA接口或YPbPr電視接口往液晶屏輸送信號的方式,這幾種顯示信號須經液晶屏的控制電路再次轉換為數字信號傳輸給液晶屏的數字掃描電路,在此過程中,信號發生器產生的數字信號經過D/A轉換、傳輸和A/D轉換,必然帶來最終圖像信號一定程度的失真與損耗。

因此本文旨在設計一種輸出數字量的信號發生器,直接經過液晶屏的LVDS接口輸入數字量的信號。

1 液晶屏的接口

本文研制的信號發生器的接收端為友達光電(AUOPTRONICS CORPORATION)生產的“M220EW01V0”型號22寬屏16:9 LCD液晶屏。

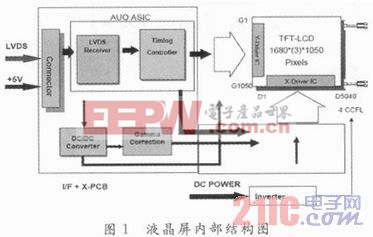

該液晶屏的邏輯控制與驅動電路對外的接口為LVDS接口。內部邏輯電路接收到LVDS輸入的差分信號后解析成LVTTL電平的圖像信號,由內部時序控制器控制產生X方向和Y方向的掃描信號,液晶屏顯示出圖像。圖1為該液晶屏內部結構圖。

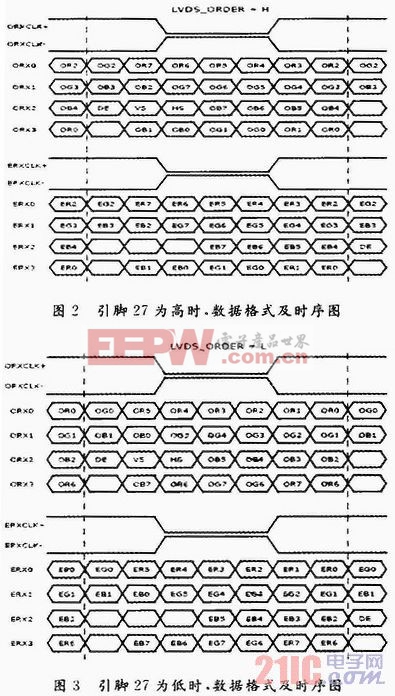

液晶屏的典型幀頻率為60 Hz,典型時鐘頻率為72.1 MHz,LVDS接口接收的數據格式與時序如圖2,圖3所示。

可以看出,通過設置引腳27為高電平或低電平,接收數據的時序有所區別。本文將27腳直接連至GND設為低電平。

以上所描述是用VHDL語言編程產生圖像時序的基礎。

2 系統整體設計

2.1 系統整體結構設計

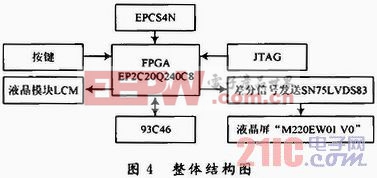

本文采用Altera公司CYCLONEⅡ系列EP2C20Q240C8 FPGA作為主控制芯片,用VHDL硬件描述語言編程,以TI公司的SN75LVDS83芯片作為差分信號發送端,將系統產生的視頻圖像信號發送給液晶屏的LVDS接口。系統還包括按鍵控制輸入模塊,用于選擇顯示的圖形模式和調整灰階值;LCM模塊YM1602C用于顯示系統的狀態信息,如圖像的灰階值等;基于Microwire協議的93C46數據存儲模塊用于存儲系統參數;另外還有FPGA的JTAG下載接口電路,及用于主動配置方式的EPCS配置芯片部分。系統結構如圖4所示。

2.2 系統難點設計

液晶屏的數據輸入口是LVDS接口,傳輸圖像數據時采用LVDS技術。LVDS(Low Voltage Differential Signaling)是一種低擺幅的差分信號傳輸技術,它使得信號能在差分PCB線對或平衡電纜上以數百Mb/s的速率傳輸,其低壓、低擺幅與低電流驅動輸出實現了低噪聲和低功耗。

TI公司生產的SN75LVDS83芯片是用于平板電視視頻傳輸的LVDS發送芯片,3.3 V供電,典型功耗250 mW,無信號傳輸時功耗小于1 mW,內含4個7 b并入串出移位寄存器,一個7倍時鐘倍頻器,共有5路LVDS驅動器,連接平衡線纜后可以同步傳輸28 b單端TTL或LVTTL數據。

FPGA產生的圖像RGB數據及同步信號并行輸入SN75LVDS83芯片,它們之間的引腳連接關系如圖5所示。系統采用了兩片SN75LVDS83芯片,分別傳輸奇像素點RGB數據和偶像素點RGB數據。

FPGA與差分信號發送電路的工作頻率要求很高,FPGA的時鐘頻率達到50 MHz,差分信號更足高達350 MHz,因此,PCB的抗高頻干擾設計是硬件設計的難點。在PCB設計中特別注意了LVDS接口的差分信號布線,數字地與模擬地的隔離問題以及信號完整性分析,同時解決了LVDS接口的阻抗匹配問題。

3 系統圖像生成設計原理及實驗結果

3.1 圖像生成設計原理

本文設計產生的圖像分三類,第一類是純彩色圖像,包括純紅、純綠、純藍和黑白圖像;第二類是方塊圖像,各方塊的色彩不同;第三類是運動圖像,圖像中有運動的元素。

在顯示第一類圖像時,只要將RGB值設定到某一組合值,無須變化,液晶屏就顯示出純彩色的圖像,在本文中還可以根據按鍵輸入修改RGB值,因此顯示的圖像灰度值就可以修改,顯示此類圖像時液晶屏表面每個像素點的RGB值都相同;顯示第二類圖像時,根據行計數器和列計數器送入不同的RGB值,就可以使液晶屏表面不同區域像素點的RGB值不相同,但這類圖像每幀都是相同的,因此是靜態圖像;RGB值除了根據行計數器及列計數器變化以外,RGB值還根據時間進行變化,這是第三類圖像產生的原理。

3.2 實驗結果

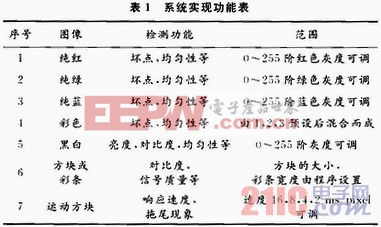

表1為本系統叮實現的圖像及檢測功能。

圖6為液晶屏顯示的可調灰度值的純紅、純綠、純藍彩色圖像。

圖7為液品屏顯示的黑白間隔的九宮格圖像。

圖8是可調節速度的方塊運動圖像截圖。顯示的圖像清晰無抖動,運動圖像中的運動方塊速度可調節并且運動穩定。

試驗測試結果表明,本信號發生器達到了設計要求,可以通過液晶屏的LVDS接口提供穩定的圖像信號。

4 結語

本文研制的LCD測試用信號發生器能夠產生測試LCD所需的各種圖像信號,通過顯示的圖像來檢測液晶屏的特性與質量。且本文研制的信號發生器在硬件設計方面克服了高頻干擾,并且產生的是純數字圖像信號,與基于AV、VGA或YPbPr信號的模擬圖像信號發生器相比,具有失真與損耗小,圖像質量好的優點,可應用于實際情況。

LCD顯示屏相關文章:lcd顯示屏原理

模擬信號相關文章:什么是模擬信號

fpga相關文章:fpga是什么

led顯示器相關文章:led顯示器原理

負離子發生器相關文章:負離子發生器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理 lcd相關文章:lcd原理 離子色譜儀相關文章:離子色譜儀原理

評論