基于FPGA的DDS基本信號發生器的設計

3.3 LCD 12864口核設計

對于Altera SOPC Builder未提供的一些外設接口模塊,用戶可以通過自定義邏輯方法在SOPC設計中添加自己開發的IP核,通過Avalon的讀寫時序對各個設備進行操作。本設計通過構建IP核來直接控制NiosⅡ和LCD12864的接口,按照指定的時序將波形參數顯示在LCD上。在SOPC Builder中自己定義component,并把液晶顯示模塊看成外部存儲器,直接做成Avalon總線Slave設備,IP核設計包含軟件部分和硬件部分,需要寫HDL模塊,定義控制狀態、數據寄存器和控制位,描述組件與Avalon總線的接口以及組件與液晶屏的接口。系統編輯器從文件中讀取I/O信號和參數信息。其次對LCD模塊進行初始化,由于SOPC Builder中的LCD12864控制模塊已經考慮了LCD的讀寫時序,所以使用NIOSⅡ IDE進行LCD驅動和控制時只需對LCD進行初始化。

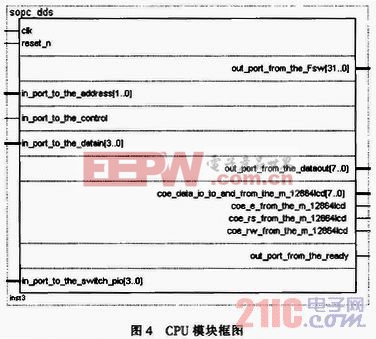

3.4 NiosⅡ嵌入式處理器系統

NiosⅡ是Altera針對其FPGA設計的嵌入式軟核處理器,它與其他IP核可構成SOPC系統的主要部分。它具有靈活的自定義指令集和自定義硬件加速單元,以及圖形化開發環境NiosⅡIDE。經由SOPC Builder生成NiosⅡ嵌入式處理器系統,其CPU模塊框圖如圖4所示。本文引用地址:http://www.czjhyjcfj.com/article/189967.htm

利用NIOSⅡIDE開發工具完成所有軟件開發任務,系統接收撥扭開關掃描模塊發來的4位掃描碼,根據掃描碼數值的不同進入不同的子程序,然后再通過FPGA的鍵盤掃描模塊向NIOSⅡ處理器發送鍵盤掃描碼,軟核處理器根據接收到的掃描碼產生相應的信號數據以及控制信號,并通過PIO傳送給FPGA中的DDS模塊,實現頻率控制字的變化,即輸出頻率可調,并將信號數據顯示在LCD上。同時DAC器件將DDS產生的8位信號數據進行數模轉換,從而產生頻率可調的方波、三角波、正弦波、鋸齒波。

4 結束語

該信號源能夠很好地滿足對不同波形、不同頻率的信號的需求,具有很強的實用性,并且可以方便地通過液晶顯示器直觀地觀察到波形信號的參數信息。由FPGA實現的DDS信號發生器不僅可實現頻率可調波形變換且具有頻率切換快,信號的質量和精度高于模擬方式的特點。

評論