基于FPGA的多功能數字鐘設計

摘要:文中簡要介紹了一種基于FPGA的多功能數字鐘設計方案。在實現數字鐘計時、校時和整點報時等基本功能的基礎上增加世界時鐘功能,能夠將北京時間快速轉換為格林威治標準時。該方案采用VHDL和原理圖相結合的設計輸入方式,在QuartusⅡ開發環境下完成設計、編譯和仿真,并在FPGA硬件開發板上進行測試,實驗證明該設計方案切實可行,對FPGA的應用和數字鐘的設計具有一定參考價值。

關鍵詞:FPGA;VHDL;數字鐘;世界時鐘;QuartusⅡ

現場可編程門陣列(Field Programmable Gate Arrays,FPGA)是一種可編程使用的信號處理器件。通過改變配置信息,用戶可對其功能進行定義,以滿足設計需求。通過開發,FPGA能夠實現任何數字器件的功能。與傳統數字電路相比,FPGA具有可編程、高集成度、高可靠性和高速等優點。

1 數字鐘總體設計

本文以FPGA平臺為基礎,在QuartusⅡ開發環境下設計開發多功能數字鐘。數字鐘實現的功能如下:

1)計時功能:進行正常的時、分、秒計時,并由6只8段數碼管分別顯示時、分、秒時間。

2)校時功能:當時校時按鍵按下時,計時器時位迅速增加,并按24小時循環;當分校時按鍵按下時,計時器分位迅速增加,并按60分循環。

3)整點報時功能:當計時到達59分53秒時開始報時,在59分53秒、55秒、57秒蜂鳴聲頻率為512 Hz;到達59分59秒為最后一聲報時,蜂鳴聲頻率為1 kHz。

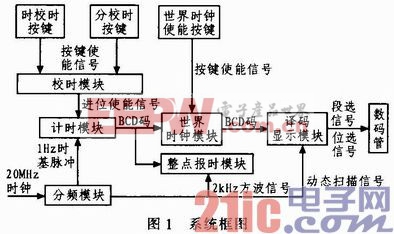

4)世界時鐘功能:默認當前顯示時間為北京時間(GMT+8),當按下世界時按鍵時,顯示時間將轉換為格林威治標準時(GMT)。數字鐘電路的模塊框圖,如圖1所示。

2 功能模塊的工作原理及設計實現

系統主要由6大模塊組成,即分頻模塊、計時模塊、校時模塊、譯碼顯示模塊、整點報時模塊和世界時鐘模塊。

2.1 分頻模塊的工作原理及設計實現

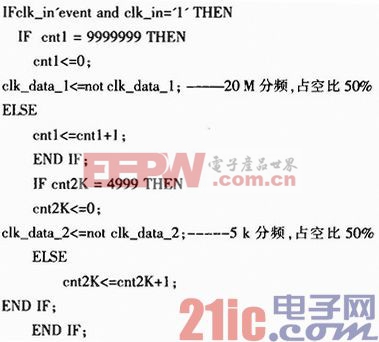

本設計選用的FPGA開發板板載20 MHz有源晶振,為了得到占空比50%的1 Hz時基脈沖及2 kHz方波信號(用于驅動譯碼顯示模塊以及為整點報時模塊提供不同頻率的信號以產生不同音調的聲音),需要對板載時鐘信號進行分頻。分頻模塊采用VHDL語言實現,對20 MHz時鐘信號分別進行兩千萬和一萬分頻。具體實現代碼如下:

2.2 計時模塊和校時模塊的工作原理及設計實現

計時模塊由60進制秒計數器、60進制分計數器和24進制時計數器級聯構成,采用同步時序電路實現。當計數器處于正常計數狀態時,3個計數器的時鐘信號均為1Hz時基脈沖,秒計數器對1 Hz的時基脈沖進行計數,其進位輸出信號cos_in作為分計數器的使能信號,而分計數器的進位輸出信號com_in又作為時計數器的使能信號。在計時模塊的基礎上,數字鐘通過增加兩個按鍵分別實現對小時和分鐘的調整。這兩個按鍵能夠產生時計數器和分計數器的另一路使能信號,即按下時校時按鍵時,時計數器使能信號持續有效,由于采用同步時序電路,時計數器能夠持續增加,達到調整時間的目的。按下分校時按鍵時原理相同。此外,校時模塊還對校時按鍵進行防抖動處理,提高系統的可靠性和抗干擾能力。

fpga相關文章:fpga是什么

塵埃粒子計數器相關文章:塵埃粒子計數器原理

評論