FPGA最小系統(tǒng)電路分析:下載配置與調(diào)試接口電路設(shè)

下載配置與調(diào)試接口電路設(shè)計(jì)

本文引用地址:http://www.czjhyjcfj.com/article/189541.htmFPGA是SRAM型結(jié)構(gòu),本身并不能固化程序。因此FPGA需要一片F(xiàn)lash結(jié)構(gòu)的配置芯片來(lái)存儲(chǔ)邏輯配置信息,用于進(jìn)行上電配置。

以Altera公司的FPGA為例,配置芯片分為串行(EPCSx系列)和并行(EPCx系列)兩種。其中EPCx系列為老款配置芯片,體積較大,價(jià)格高。而EPCSx系列芯片與之相比,體積小、價(jià)格低。

另外,除了使用Altera公司的配置芯片,也可以使用Flash+CPLD的方式去配置FPGA。

在把程序固化到配置芯片之前,一般先使用JTAG模式去調(diào)試程序,也就是把程序下載到FPGA芯片上運(yùn)行。雖然這種方式在斷電以后程序會(huì)丟失,但是充分利用了FPGA的無(wú)限擦寫(xiě)性。

所以一般FPGA有兩個(gè)下載接口:JTAG調(diào)試接口和AS(或PS)模式下載接口。所不同的是前者下載至FPGA,后者是編程配置芯片(如EPCSx),然后再配置FPGA。

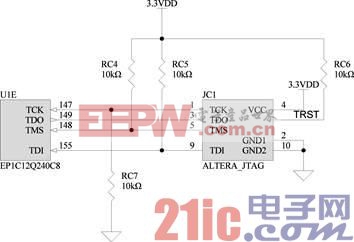

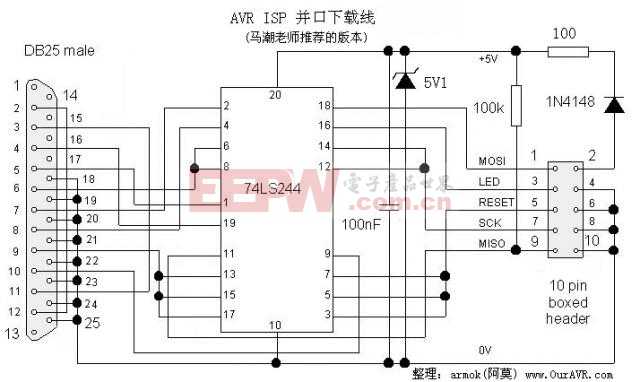

如圖2.7和圖2.8所示分別是JTAG模式和AS模式的電路原理圖。

圖2.7 JTAG模式原理圖

評(píng)論