基于流水線加法器的數字相關器設計

O 引言

數字相關器是擴頻通信體制下數字中頻接收機核心部件之一,在數字擴頻通信系統中應用廣泛,但由于受數字信號處理器件速度限制,無法應用于高速寬帶通信系統。其中一個重要原因是高位數的加法器進位延遲過大,使得在一個采樣時鐘節拍內無法完成一次累加運算,而導致相關運算錯誤。隨著FPGA技術的快速發展,器件速度的不斷提升,這一問題一定程度得到改善,但仍然無法滿足高位數擴頻碼、高采樣速率和大動態范圍的數字相關器的工程實現,因此必須采用優化算法最大限度地減少加法器進位操作,從而降低電路延遲對數字相關處理的影響,較為可行的方法是通過流水線加法器構建數字相關器。

1 數字相關器基本模型分析

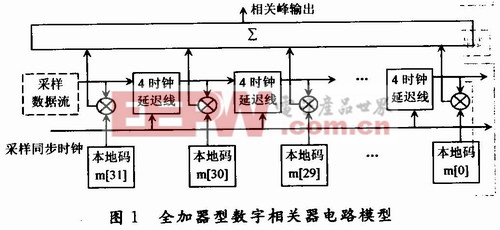

數字相關器類似于匹配濾波器,可以看作乘累加運算器,即輸入數據流同本地碼在采樣同步時鐘的驅動下(在一個時鐘節拍內)逐級相乘并累加。以32階數字相關器為例,假定中頻信號采樣速率是擴頻碼速率的4倍,輸入采樣數據流為補碼(如果輸入碼流是2進制碼應通過邏輯電路轉換成補碼),可建立如圖1所示電路模型(全加器型)。

圖1所構建的數字相關器其特點是模型較為簡單,在進行FPGA邏輯電路設計時也較容易實現,同時在輸入信號動態范圍較小(采樣數據流數據帶寬較小)的情況下器對硬件資源的消耗也較少(不考慮乘法器消耗的資源)。但是當輸入信號動態范圍較大時,如采樣數據流數據帶寬超過8 b,中頻信號采樣速率超過40 MHz時此模型的缺陷就會暴露出來,其核心問題是∑求和加法電路要在一個時鐘節拍內必須完成32個8 b補碼數據的加法運算,而FPGA內部門到門的延遲會使每一位加法電路在進行運算時產生一定時間的暫態。當這種暫態逐級累加時就會造成一個時鈍單位內無法產生穩定、有效的輸出結果,同時如果輸入的數據流產生較多的進位,則會使相關結果出錯。

由上述可知,圖1所描述的相關器電路模型應用在實際的通信系統中會存在隱患,尤其是作為時隙信號同步頭字符相關處理時,有可能造成時隙同步的誤觸發。若作為位同步字符時會造成整時隙的接收數據較高誤碼。

評論