基于DP標(biāo)準(zhǔn)發(fā)射端擴頻時鐘發(fā)生器電路設(shè)計

引言

本文引用地址:http://www.czjhyjcfj.com/article/187197.htmDP(DisplayPort)接口標(biāo)準(zhǔn)旨在尋求代替計算機的數(shù)字視頻接口DVI、LCD顯示器的低壓差分信號LVDS(Low Voltage Differential Signal)。DP利用目前交流耦合電壓差分的PCI Express電氣層,有1~戽?zhèn)€工作速率為217 Gb/s的數(shù)據(jù)對(Lanes),最高可獲得4通道多達10.8 Gb/s的帶寬。時鐘不是分離的,而是內(nèi)置于Lanes。傳輸命令和控制的輔助數(shù)據(jù)通道是雙向的,最高傳輸比特率可達1 Mb/s。DP支持的最大傳輸距離為15 m,而其工作電平比DVI更低。

伴隨微處理器的頻率不斷增加,由此產(chǎn)生的電磁干擾會影響電子產(chǎn)品的正常。為了抑制電磁干擾,人們先后研究出屏蔽、脈沖整形、濾波、低電壓差分時鐘、特殊版圖布局、擴頻時鐘發(fā)生器等方法,其中擴頻時鐘發(fā)生器可有效減小峰值和諧波的功率,且可通過電路設(shè)計的廣闊空間實現(xiàn),因而得到廣泛應(yīng)用。這里設(shè)計一種基于DP標(biāo)準(zhǔn)采用μ工藝的發(fā)射端擴頻時鐘發(fā)生器。合理設(shè)計鎖相環(huán)路,采用外加濾波器對壓控振蕩器的控制電壓進行三角波調(diào)制,得到所需的擴頻時鐘。

2 擴頻時鐘發(fā)生器總體結(jié)構(gòu)

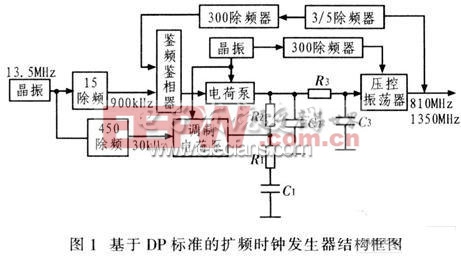

降低電磁干擾(EMI)是電子系統(tǒng)設(shè)計人員需要考慮的重要因素,擴頻時鐘(CLK)為降低EMI提供一個有效途徑。這里采用tsmc0.18μm 工藝設(shè)計一款符合DisplayPort標(biāo)準(zhǔn)發(fā)射端的擴頻時鐘發(fā)生器。在合理設(shè)計鎖相環(huán)路的基礎(chǔ)上,運用外加電荷泵對壓控振蕩器的控制電壓進行三角波調(diào)制,得到所需要的擴頻時鐘。圖1為該設(shè)計結(jié)構(gòu)框圖。

3 各模塊電路設(shè)計

3.1 鑒頻鑒相器電路

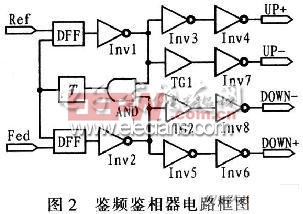

圖2為鑒頻鑒相器電路框圖。鑒頻鑒相器的輸出由輸入信號的頻率和相位決定,它比較兩個輸入信號的上升沿,當(dāng)輸入?yún)⒖紩r鐘信號Ref的上升沿超前反饋信號Fed的上升沿到達鑒頻鑒相器時,鑒頻鑒相器的輸出UP為高,而此時DOWN保持為低電平,當(dāng)Fed的上升沿也到來時,輸出被復(fù)位;當(dāng)信號Fed的上升沿超前參考信號Ref到來時,輸出DOWN為高,當(dāng)Ref的上升沿也到來時,鑒頻鑒相器被復(fù)位。因此,鑒頻鑒相器根據(jù)輸入信號相位差來驅(qū)動后級電路。比較兩個輸入信號的相位差,然后將其轉(zhuǎn)變成兩個數(shù)字信號來控制電荷泵的工作狀態(tài)。在本設(shè)計中,由于參考輸入頻率僅為900 kHz,因而對鑒頻鑒相器的工作速度要求并不高。因此,在滿足低功耗要求的前提下,采用最簡單的無死區(qū)鑒頻鑒相器的結(jié)構(gòu)。

為了避免死區(qū),在復(fù)位路徑中引入延時T。在設(shè)計延時時長時,首先應(yīng)考慮鑒頻鑒相器的工作頻率。因為鑒頻鑒相器的最高丁作頻率為1/2Tdelay,Tdelay包括插入延時和鑒頻鑒相器的內(nèi)部延時。要求插入延時的引入不影響鑒頻鑒相器的正常工作;另外需考慮當(dāng)插入延時相對較長時,電荷泵的充、放電電流同時開啟的時間就會變長,而電荷泵存在的失調(diào)就會在濾波器電容上引入抖動,即增加鎖相環(huán)輸出的雜散成分。因此,在鑒頻鑒相器內(nèi)部延時可忽略及充分開啟電荷泵的前提下,應(yīng)盡量減小失調(diào)。這里插入延時取8 ns。由于后級電荷泵電路為差分輸入,因此采用傳輸門減少反相器的延時。

3.2 帶隙基準(zhǔn)電路

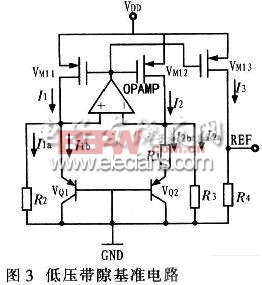

為滿足帶隙基準(zhǔn)電路的低壓應(yīng)用,這里采用一種電流模式結(jié)構(gòu)的低壓帶隙基準(zhǔn)電路,如圖3所示。該電路可以輸出低于1 V的電壓,有效降低了電路的電源電壓;同時,電路中采用與電壓無關(guān)的偏置及帶負(fù)反饋網(wǎng)絡(luò)的二級運放,降低了電路的電源敏感性。

基于0.35μm CMOS工藝的HSPICE仿真結(jié)果表明,該電路可工作在1.1~1.5 V的低電源電壓下,并具有14 ppm/℃的低溫度系數(shù),能夠輸出200 mV~1.25 V的寬范圍電壓,并使用與電源無關(guān)偏置以及帶負(fù)反饋網(wǎng)絡(luò)的二級運放,提高輸出電壓的精度,該電路中,各MOS管都工作于飽和狀態(tài)。電路中運算放大器采用二級結(jié)構(gòu),具有較高的低頻增益。

評論