Lattice ECP3 FPGA評估板解決方案

Lattice公司的LatticeECP3 FPGA系列可提供高性能特性如增強的DSP架構,高速SERDES和高速源同步接口。LatticeECP3采用65nm技術,查找表(LUT)高達149k邏輯單元,支持高達486個用戶I/O,提供高達320個18×18乘法器和各種并行I/O標準,主要用于對成本和功耗敏感的無線基礎設備和有線通信。

本文引用地址:http://www.czjhyjcfj.com/article/186626.htmFPGA器件的LatticeECP3系列經過優化來提供高器件的性能,如增強的DSP架構,高速SERDES,和經濟型FPGA架構,高速源同步接口。這種組合是通過器件架構的進步,和65nm技術的使用而完成的,這就使得其設備適合高容量、高速度和低成本的要求。 LatticeECP3器件系列使得查找表(LUT)的容量擴大至149k邏輯單元,并支持多達486個用戶I/ O。

LatticeECP3器件系列還提供了多達320個18×18乘法器和廣泛的并行I/O標準。LatticeECP3 FPGA架構進行了優化,目的是提高性能和降低成本。LatticeECP3器件采用可重構SRAM邏輯技術,并提供了深受歡迎的構件,如基于LUT的邏輯,分布式的嵌入式存儲器,鎖相環(PLL),延遲鎖定環(DLL),預制的源同步I-/ O支持,增強的sysDSP片以及先進的配置支持,包括加密和雙啟動功能。

在LatticeECP3系列上應用的、預設計的源同步邏輯支持廣泛的接口標準,包括DDR3,XGMII和7:1 LVDS。 LatticeECP3器件系列還具有專門用于PC功能的高速SERDES。高抖動容限和低傳輸抖動使得SERDES+PCS塊可以進行配置,以支持流行的數據協議,包括PCI Express,SMPTE,以太網(XAUI,千兆以太網和SGMII)和CPRI。發送預加重和接收均衡設置使得SERDES非常合適各種形式的媒體傳輸和接收。

LatticeECP3器件還提供靈活,可靠和安全的配置選項,如雙啟動,比特流加密和TransFR現場升級功能。Lattice的ispLEVER設計工具套件,通過使用LatticeECP3 FPGA系列,可以使得大型復雜的設計更加有效地實施。支持LatticeECP3的綜合資料庫可以提供給工程師,以便邏輯綜合工具的使用。

ispLEVER工具采用了結合型工具輸出(避免板上平面圖設計工具的制約)來設計LatticeECP3器件的路線和布局。ispLEVER工具從路由中提取時序,并詮釋成設計,用以驗證時序。Lattice公司為LatticeECP3系列提供了許多預先設計的IP(知識產權) ispLeverCORE模塊。采用這些可配置的軟核IP作為標準化的模塊,設計師們可以沒有后顧之憂地專注于他們的獨特設計,以增加效率。

圖1 Lattice ECP3 AMC評估板外形圖

LatticeECP3 FPGA主要特性

更高的邏輯密度,提高了系統集成度

•17k~149k的LUT

•133~586個I / O

嵌入式SERDES

•150 Mbps~3.2 Gbps用于Generic 8b10b,10位SERDES和8位SERDES模式

•其他協議每通道數據傳輸速率230 Mbps~3.2 Gbps

•每個設備最多16個通道,PCI Express,SONET / SDH,以太網(1GbE,SGMII XAUI),CPRI,SMPTE 3G和Serial RapidIOsysDSP

•全級聯片結構

•12到160片高性能乘法和累加

•強大的54位ALU操作

•時分復用MAC共享

•舍入和截斷

•每片支持

-半個36×36,兩個18×18,或四

個9×9乘法器

-先進的18×36 MAC和18x18乘法乘法累加(MMAC)操作靈活的內存資源

•最多6.85Mbits的sysMEM 嵌入式RAM塊(EBR)

• 36k~303k位分布式RAMsysCLOCK模擬PLL和DLL

•兩個DLL,和每個設備多達10個鎖相環預加工源同步I/O

• I/O單元里的DDR寄存器

圖2 Lattice ECP3 AMC接口板外形圖

•專用的讀/寫平衡功能

•專用齒輪邏輯

•源同步標準的支持

- ADC/DAC,7:1 LVDS,XGMII高速ADC/ DAC器件

•專用DDR/DDR2/DDR3內存,支持DQS

•校正輸出可選的符號間干擾(ISI)可編程sysI/O的緩沖區支持多種接口

•片上終止

•可選輸入均衡濾波器

• LVTTL和LVCMOS33/25/18/15/12

• SSTL 33/25/18/15 I,II

• HSTL15 I 和HSTL18 I,II

• PCI和差分HSTL,SSTL

• LVDS, Bus-LVDS,LVPECL,RSDS,MLVDS靈活的設備配置

•專用庫用于配置I/O

• SPI引導閃存接口

•雙啟動圖像支持

•從SPI TransFR的I/O用于簡單現場更新

•軟錯誤檢測嵌入宏系統級支持

• IEEE 1149.1和IEEE 1532兼容

• Reveal邏輯分析器

• ORCAstra FPGA配置實用程序初始化與一般使用的片上振蕩器

• 1.2V核電源

Lattice ECP3 AMC評估板

LatticeECP3高級夾層卡(AMC)評估板可以使設計師們在AMC系統環境中對LatticeECP3高速SERDES收發器的功能進行調查和實驗。LatticeECP3 AMC評估板可以協助設計師們進行快速的原型設計,并測試他們的設計。該評估板具有PICMG AMC R2.0 AMC的外形尺寸規格,可以使用戶在現場系統評估。本用戶指南要參考評估設計教程來使用,以更好地了解LatticeECP3 FPGA。

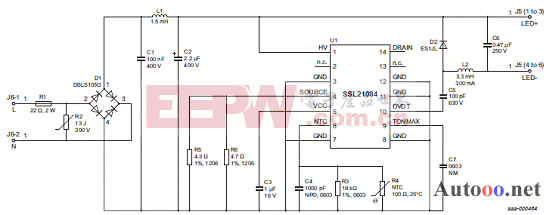

圖3 Lattice ECP3 AMC評估板電路圖(1)

Lattice ECP3 AMC評估板主要特性

•單模塊AMC PCB卡邊緣接口

-可以示范AMC Fat Pipes

-常見的接口選項

•可以使用串行客戶端接口來控制SERDES PCS寄存器(ORCAstra)

• DMC(FPGA夾層卡)擴展接口

• USB-B連接到UART用以運行時間控制

• RJ45接口至10/100/1000以太網至SGMII

• SFP收發器模塊籠和連接

•板上引導閃存

- 64M串行SPI閃存

• DDR2內存組件(256×32位)

• 32位并行,非易失性內存,可以讀取,

擦除和重新編程

•開關,指示燈和顯示器,用于演示

• ispVM系統軟件編程支持

•板上參考時鐘源

評論