一種用于高速高精度ADC的電壓基準源設計

隨著集成電路規模不斷擴大,尤其是芯片系統集成技術的提出,對模擬集成電路基本模塊(如A/D、D/A轉換器、濾波器以及鎖相環等電路)提出了更高的精度和速度要求,這也就意味著系統對其中的基準源模塊提出了更高的要求。

用于高速高精度ADC的片內電壓基準源不僅要滿足ADC精度和采樣速率的要求,并應具有較低的溫度系數和較高的電源抑制比,此外,隨著低功耗和便攜的要求,ADC也在朝著低壓方向發展,相應的基準源也要滿足低電源電壓的要求。

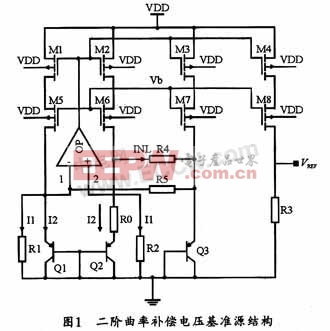

本文分析了基準源對流水線ADC精度的影響,并建立了相應的模型,確定了高速高精度ADC對電壓基準源的性能要求。給出了基于1.8 V的低電源電壓,并采用結構簡單的VBE非線性二階補償帶隙基準源的核心電路,該補償方式可以實現較低的溫度系數,能滿足高速高精度ADC的要求。箝位運放采用一種低噪聲兩級運算放大器,該運放可提供小于0.02 mV的失調電壓,因而保證了基準源的補償精度。為了提高基準源的電源抑制比,本文除采用常用的共源共柵電流鏡技術以外,還設計了一種簡單有效的電源抑制比提高電路,從而使得基準源的電源抑制比有了較大提高。

1 電壓基準源影響的建模分析

在Pipelined ADC系統中,基準源的主要作用是為子ADC提供比較電平,同時為MDAC提供殘差電壓。差分基準電壓源發生偏移會導致子ADC比較電平和MDAC殘差電壓發生變化。而通過引入冗余位矯正技術可大大減小差分基準電壓源所引起的比較電平變化對系統指標造成的影響,但是,MDAC殘差電壓變化的影響卻無法消除,系統的轉移特性曲線仍將會發生變化,從而造成系統指標下降。其中基準電壓源的偏移主要來源于溫度和電源電壓的影響。

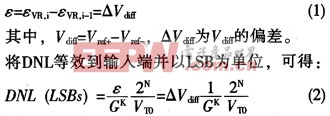

下面分析基準電壓源溫度漂移特性對DNL的影響。一般情況下,實際相鄰輸出與理想相鄰輸出之間的偏差可以表示為:

對于首級精度為3.5位的12位ADC,在-40℃~85℃的溫度范圍內,對溫度要求最嚴格的比較器一般要求基準電壓源的最大溫漂不超過(7/8)Vdiff。

根據下列兩式:

可以得到DNL對基準電壓源溫度系數的要求,即溫度系數TC≤6.84 ppm/℃。式中,VT0為室溫25℃時的基準電壓值。

2電壓基準源電路結構設計

2.1 二階曲率補償技術

由前文分析可知,12位ADC系統要求溫度系數應小于6.84ppm/K才能達到12位精度。傳統帶隙基準源很難達到這個要求,因此,本文選用一種如圖1所示的二階曲率補償的電壓基準源結構。

如圖1所示,根據VBE的溫度關系式:

評論