數字控制挑戰傳統電源設計理念VMC、CMC

電源設計之初所要求的基本決定之一是:采用電壓模式控制(VMC)還是采用電流模式控制(CMC)。對任何設計而言,交易存在于兩個執行方法之間。然而,由于數字控制方法的引入,這些已被嘗試并值得信賴的交易正面臨著嚴峻挑戰。本文將研究這條繪制的主線,以及數字控制是如何在是否采用VMC還是采用CMC的交鋒中成為一種不可阻擋的再認知的。

本文引用地址:http://www.czjhyjcfj.com/article/180182.htm方法

大量詳實的材料充分的描述了電流模式控制和電壓模式控制,因此本文只作一下簡單的回顧。VMC由單個控制環路組成,該環路采用輸出電壓作為反饋信號。輸出電壓改變之后環路重新動作產生一個瞬時響應去替換。由于我們的目標是要維持一個恒定輸出電壓,因此緩慢響應是一個明顯的缺陷。CMC添加了一個外部反饋環路。除電壓控制環路外,它還對電流流向敏感以及對峰值電流到達時電源開關的關斷動作敏感。電流信號作為主要的控制環路。也許有人會認為VMC和CMC比較會有更緩慢的響應,但這種觀點是不正確的,因為環路響應最終是由系統帶寬決定的。兩種方法都可以設計出相同的環路帶寬,因此VMC并不一定必然比CMC慢。

克服VMC問題

由此,讓我們研究一下傳統觀念,即為何VMC或CMC會成為首選方案。在推挽或全橋式電路拓撲中,流向開關電路兩個管腳的電流也許并不總是相等。這將會導致FET失衡或定時錯誤。其網絡影響是會在變壓器上產生直流建立,這將會迅速的導致變壓器核飽和。傳統的方法是采用一個電容和主變壓器串聯起來。

該直流阻塞電容可耦合交流信號,這樣可以阻止變壓器核的飽和。這樣做的缺點是要和主電源路徑串聯,因此它必定是一個可靠器件。要求可供1kW電源使用、10uF等級的阻塞電容的額定值必定要超過全電壓波動。而且,變壓器通常都要采用冗余設計來抑制飽和。由于CMC的控制環路在超過兩個管腳相同電流極限時關斷了電源開關,因此CMC并不會因此表象受損。這意味著變壓器中沒有直流電流建立。

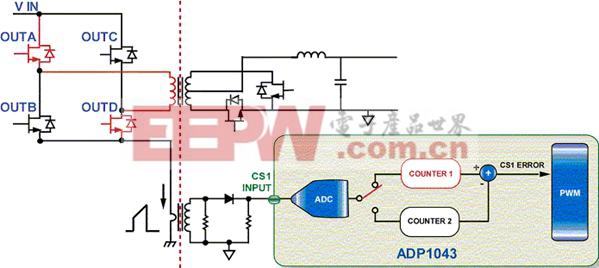

圖1描述了數字控制是如何解決這個問題的。控制器測量每個半橋電路的電流并計算其差值。差值信號驅動主PWM信號對失衡進行補償。從概念上來說,此方法和CMC是相似的,這可以視為平均CMC而不是峰值CMC。

圖1:帶有集成電壓次級平衡電路的數字控制器。

環路穩定性和濾波

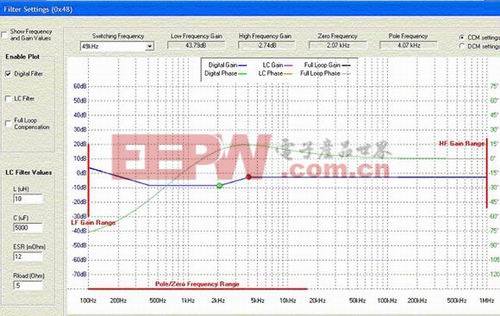

由于CMC環路近似為單極性滾輪(每十年-20°dB)的控制輸出傳遞功能,所以通常認為穩定CMC環路要比穩定VMC環路要容易。VMC環路近似為雙極性滾輪(每十年-40°dB)的傳遞控制,這樣使得補償網絡變得更加復雜。在另外一個領域里,數字控制在這場交鋒中呈現出了一個全新面貌。用戶友好型的圖形用戶接口(GUI)的出現意味著環路補償已成為了簡單任務。設計者輸入所需的濾波器響應,GUI就會計算濾波器實現響應所需的系數。不僅一個良好設計的GUI去掉了外部復雜性,而且也前進了一大步,因為它使得整個補償程序比以前簡單了很多。

圖2:濾波器補償圖形用戶接口。

評論