應(yīng)用于負電源的電平位移電路及器件設(shè)計

摘要:本文設(shè)計了一種應(yīng)用于負電源的電平位移電路。實現(xiàn)從0~8V低壓邏輯輸入到8~-100V高壓驅(qū)動輸出的轉(zhuǎn)換。分析了該電路的結(jié)構(gòu)和工作原理。基于此電路結(jié)構(gòu)設(shè)計了滿足應(yīng)用要求的高壓薄膜SOI LDMOS器件。分析了器件的工作狀態(tài)以及耐壓機理,并利用工藝器件聯(lián)合仿真對器件的電學特性進行了優(yōu)化設(shè)計。

關(guān)鍵詞:電平位移;薄膜SOI;LDMOS;負電源;開態(tài)擊穿電壓

隨著智能功率IC的發(fā)展.其應(yīng)用領(lǐng)域和功能都在不斷地擴展。而作為智能功率IC中的重要一類柵驅(qū)動IC在功率開關(guān)、顯示驅(qū)動等領(lǐng)域得到廣泛應(yīng)用。在柵驅(qū)動電路中需要電平位移電路來實現(xiàn)從低壓控制輸入到高壓驅(qū)動輸出的電平轉(zhuǎn)換。而在一些領(lǐng)域如SOC中的待機模式激活、ESD保護等需要能工作在負電源的電平位移電路。

SOI(Silicon-On-Insulator)技術(shù)以其高速、低功耗、高集成度、極小的寄生效應(yīng)以及良好的隔離等特點,在集成電路設(shè)計應(yīng)用中倍受青睞。其優(yōu)良的介質(zhì)隔離性能使得智能功率IC中高低壓器件的隔離更為完善。

本文基于SOI高壓集成技術(shù)設(shè)計了電源電壓為8~-100V的電平位移電路,并對電路中的核心LDMOS器件進行了設(shè)計和模擬仿真優(yōu)化。

1 電路結(jié)構(gòu)

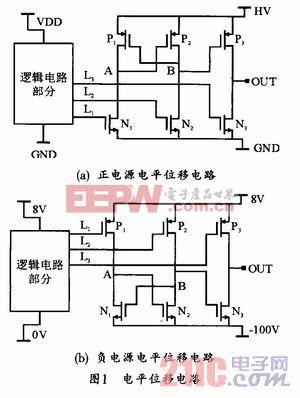

傳統(tǒng)正電源應(yīng)用的電平位移電路結(jié)構(gòu)如圖1(a)所示。L1、L2、L3是由邏輯電路部分產(chǎn)生的低壓時序控制信號,N1、N2、N3為高壓nLDMOS器件,P1、P2、P3為高壓平pLDMOS器件。由P1,P2和N1、N2構(gòu)成的電平位移單元將L1、L2的低壓邏輯信號轉(zhuǎn)變?yōu)榭梢钥刂芇3管的高壓電平,與L3一起控制由P3和N3組成的反向輸出級,從而實現(xiàn)從低壓邏輯信號到高壓驅(qū)動輸出的轉(zhuǎn)換。

在正電源電平位移電路中,由于nLDMOS的源極為低壓,所以可以通過低壓邏輯部分來控制其開關(guān)狀態(tài),而源極為高壓的pLDMOS則通過電平位移來控制。當高壓驅(qū)動電壓為8~-00V,低壓邏輯部分工作電壓為0~8V時,電平位移轉(zhuǎn)換部分的電壓分布本身沒有改變,但是在和低壓控制端接合時,與傳統(tǒng)的正電源相比電平發(fā)生了改變,就需要重新設(shè)計低壓邏輯的控制方式。此時,nLDMOS的源極為-100V電壓,顯然不能通過低壓邏輯控制部分的0~8V電壓來實現(xiàn)控制,而pLDMOS的源極為8V電源。因此采用了低壓邏輯輸出直接控制pLDMOS,而nLDMOS則通過電平位移來控制的方法,如圖1(b)所示。

DIY機械鍵盤相關(guān)社區(qū):機械鍵盤DIY

評論