基于二叉樹的CVSL電路優化方法

摘要:CVSL,電路不同于互補CMOS邏輯那樣具有固定的構成規則,對于復雜邏輯,若不對電路進行優化,則電路速度、版圖面積、功耗等性能指標均會受到影響。因此用一種方法有規律的來完成CVSL,電路結構的設計顯得十分重要,傳統的卡諾圖化簡法步驟過多,結構不夠直觀,鐘對這一缺陷,提出了用二叉樹代替傳統的卡諾圖法的設計思路,從而使CVSL電路結構得到優化。分析結果表明,二叉樹優化法較卡諾圖法可使電路獲得了更加高效的設計結果。

關鍵詞:電路結構優化;二又樹優化法;CVSL電路;互補CMOS邏輯

0 引言

CVSL電路適合于整個系統或模塊的高速設計中。在單端式邏輯(Single-ended logic)和差動式邏輯間需要提供互補信號的反相器。對于復雜邏輯,由于兩個NMOS Tree有共同項,電路可進一步化簡,減少MOS管數量。傳統的方法是用卡諾圖法,但卡諾圖并不能顯示出電路的連接關系,若改用二叉樹算法,則可以很明了的反映出電路的連接關系。

1 CVSL電路的特點

互補靜態CMOS特點電路的特點是P管陣列的邏輯結構正好是N管陣列的對偶,若一陣列是串聯,則另一陣列必定是并聯。NMOS陣列是原量控制,PMOS陣列是非量控制,因而,N型陣列和P型陣列可以接同一個輸入信號。電路中PMOS管的數目與NMOS管的數目相同。如果輸入變量共有k個,則總共需要2k個晶體管,形成一種全互補電路。但管子數量多,版圖可能比較復雜。只有設計得當,版圖才會有規則。

雖然CMOS電路有許多優點,但一般認為其與偽NMOS相比有兩大缺點:

(1)CMOS電路的速度比偽NMOS低。任何一級CMOS倒相器至少有兩只管子,一只P管和一只N管,它們的柵極是連接在一起的,輸入電容加倍,前級的充放電就比較慢。

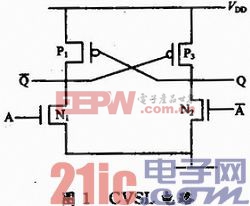

(2)CMOS電路所需的器件數多。一個邏輯電路需要設計兩套邏輯函數,分別傳送原函數和其補函數。因而,CMOS電路的邏輯冗余度較高。不僅浪費硅片面積,而且增加互聯任務,使性能降低。偽NMOS電路只采用一個P管作為上拉負載,以代替全互補標準CMOS電路中的P陣列邏輯。但增加了靜態功耗,提高了輸出低電平,降低了噪聲容限。為克服功耗提出電路的改進方案即CVSL電路,如圖1所示。

由于電路同時接收差動式的輸入(Differential Input)且提供差動式的輸出(Differential Outputs),所以又稱為DCVSL(Differential Cascade Voltage SwitchLogic)電路。并且原量反量同時輸出。雖然比CMOS所用MOS管數量多,但提供互補輸出且由于電子遷移率高于空穴,相同面積下速度比CMOS高(是一種高速設計)。由于存在正反饋,完全消除了Pseudo-NMOS中的靜態電流,使輸出達到rail to rail(低功耗高噪聲容限),進一步提高了翻轉速度。

該電路適合于整個系統或模塊都用DCVSL,的設計,在單端式邏輯(Single-ended Logic)和差動式邏輯間需要提供互補信號的反相器。對于復雜邏輯,由于兩個NMOS Tree有共同項,所以電路可進一步化筒,減少了MOS管數量。

評論