MCS-51單片機與FPGA

1 單片機與FPGA的接口方式單片機與FPGA的接口方式一般有兩種,即總線方式與獨立方式。MCS-51單片機具有很強的外部總線擴展能力,利用片外三總線結構很容易實現單片機與FPGA的總線接口,而且單片機以總線方式與FPGA進行數據與控制信息通信也有許多優點:速度快;節省PLD芯片的I/O口線;相對于非總線方式,單片機編程簡捷,控制可靠;在FPGA中通過邏輯切換,單片機易于與SRAM或ROM接口。

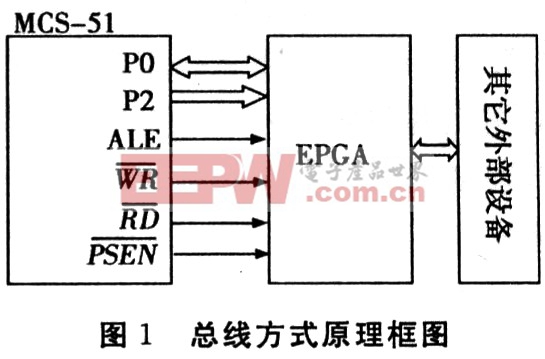

本文引用地址:http://www.czjhyjcfj.com/article/173230.htm單片機與FPGA以總線方式通信的邏輯設計,重要的是要詳細了解單片機的總線讀寫時序,根據時序圖來設計邏輯結構,其通信的時序必須遵循單片機內固定的總線方式讀/寫時序。FPGA的邏輯設計也相對比較復雜,在程序設計上必須與接口的單片機程序相結合,嚴格安排單片機能訪問的I/O空間。單片機以總線方式與FPGA進行數據通信與控制時,其通信工作時序是純硬件行為,速度要比前一種方式快得多,另外若在FPGA內部設置足夠的譯碼輸出,單片機就可以僅通過19根I/O線在FPGA與單片機之間進行通信和控制信息交換,這樣可以節省FPGA芯片的I/O線。其原理圖如圖1所示。

2 總線接口邏輯設計

2.1 接口設計思想

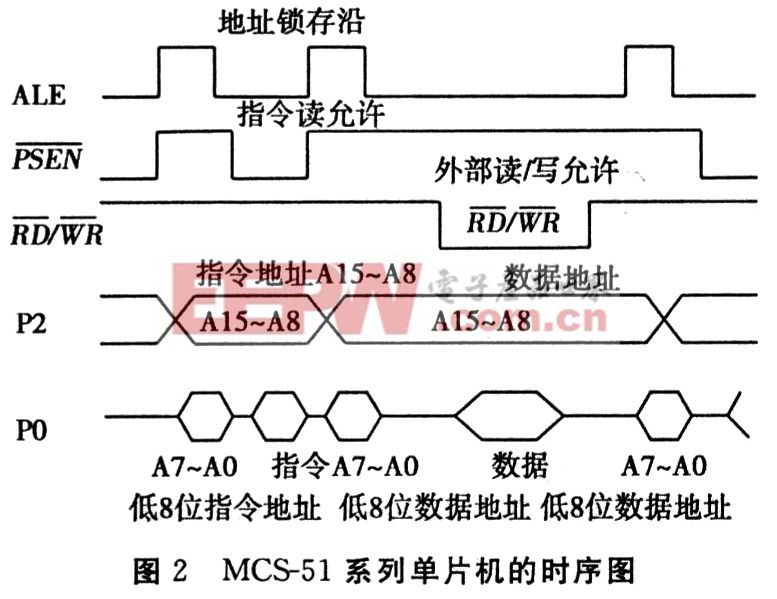

單片機與CPLD/FPC,A以總線方式通信的邏輯設計,重要的是要詳細了解單片機的總線讀寫時序,根據時序圖來設計邏輯結構。MCS-51系列單片機的時序圖如圖2所示。

ALE為地址鎖存使能信號,可利用其下降沿將低8位地址鎖存于FPGA中的地址鎖存器(LATCH_ADDRES)中;當ALE將低8位地址通過P0鎖存的同時,高8位地址已穩定建立于P2口,單片機利用讀指令允許信號PSEN的低電平從外部ROM中將指令從P0口讀入,由時序圖可見,其指令讀入的時機是在PSEN的上升沿之前。接下來,由P2口和P0口分別輸出高8位和低8位數據地址,并由ALE的下降沿將P0口的低8位地址鎖存于地址鎖存器。若需從FPGA中讀出數據,單片機則通過指令“MOVXA,@DPTR”使RD信號為低電平,由P0口將鎖存器中的數據讀入累加器A;但若欲將累加器A的數據寫進FPGA,則需通過指令“MOVx DPTR,A”和寫允許信號WR。這時,DPTR中的高8位和低8位數據作為高、低8位地址分別向P2和P0口輸出,然后由WR的低電平并結合譯碼,將累加器A的數據寫入圖中相關的鎖存器。

評論